# **Digital Systems Design**

Ramaswamy Palaniappan

Ramaswamy Palaniappan

### **Digital Systems Design**

Digital Systems Design © 2011 Ramaswamy Palaniappan & Ventus Publishing ApS ISBN 978-87-7681-806-7

### Contents

|     | Preface                                              | 7  |

|-----|------------------------------------------------------|----|

|     | About the author                                     | 8  |

| 1   | Number System Basics                                 | 9  |

| 1.1 | Decimal Numbers                                      | 9  |

| 1.2 | Other Number Systems – Binary, Octal and Hexadecimal | 10 |

| 1.3 | Conversion between different number systems          | 13 |

| 1.4 | Other number codes                                   | 15 |

| 2   | Introduction to Logic Gates                          | 19 |

| 2.1 | AND gate                                             | 22 |

| 2.2 | OR gate                                              | 25 |

| 2.3 | NOT gate                                             | 27 |

| 2.4 | AND implementation with OR gate and vice versa       | 28 |

| 2.5 | NAND gate                                            | 29 |

| 2.6 | NOR gate                                             | 31 |

| 2.7 | Integrated circuits                                  | 32 |

Please click the advert

Download free ebooks at bookboon.com

#### Contents

© UBS 2010. All rights reserved.

| 3   | Combinatorial Logic Circuits          | 33 |

|-----|---------------------------------------|----|

| 3.1 | Logic circuit simplification          | 34 |

| 3.2 | Boolean algebra                       | 35 |

| 3.3 | DeMorgan's theorem                    | 38 |

| 3.4 | More examples                         | 39 |

| 3.5 | XOR and XNOR gates                    | 43 |

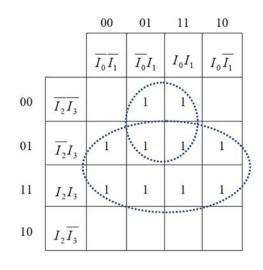

| 4   | Karnaugh Maps                         | 47 |

|     |                                       |    |

| 4.1 | Sum of products                       | 47 |

| 4.2 | Product of sums                       | 48 |

| 4.3 | K-maps                                | 51 |

| 5   | Bistable Multivibrator Circuits       | 67 |

| 5.1 | S-R flip-flop                         | 68 |

| 5.2 | J-K flip-flop                         | 75 |

| 5.3 | D flip-flop                           | 79 |

| 5.4 | T flip-flop                           | 82 |

| 5.5 | Monostable and astable multivibrators | 84 |

|     |                                       |    |

### You're full of *energy and ideas*. And that's just what we are looking for.

Looking for a career where your ideas could really make a difference? UBS's Graduate Programme and internships are a chance for you to experience for yourself what it's like to be part of a global team that rewards your input and believes in succeeding together.

Wherever you are in your academic career, make your future a part of ours by visiting www.ubs.com/graduates.

www.ubs.com/graduates

#### Contents

| 6   | Arithmetic Circuits                          | 87  |

|-----|----------------------------------------------|-----|

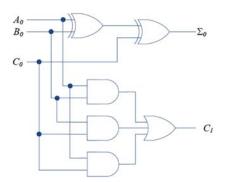

| 6.1 | Half adder                                   | 87  |

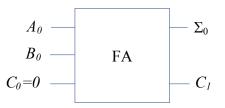

| 6.2 | Full adder                                   | 89  |

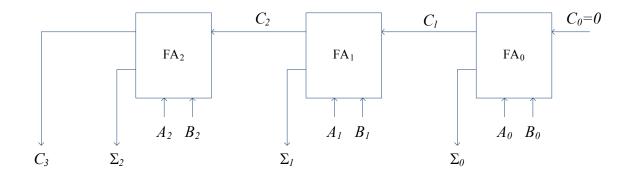

| 6.3 | Parallel adder                               | 92  |

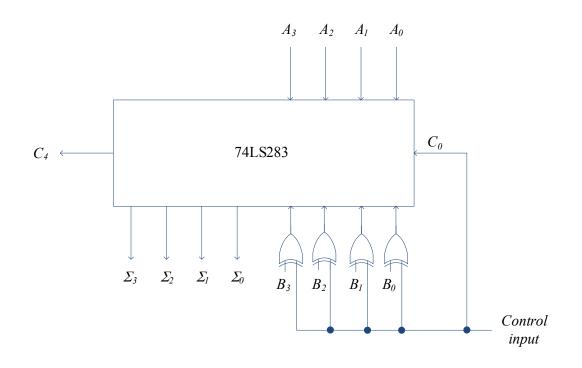

| 6.4 | Parallel addition using integrated circuits  | 93  |

| 6.5 | Parallel subtraction                         | 94  |

| 7   | Coders and Multiplexers                      | 98  |

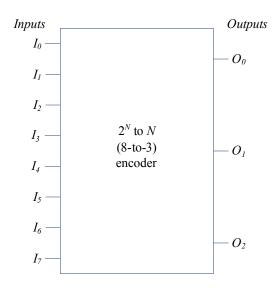

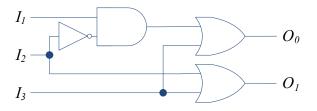

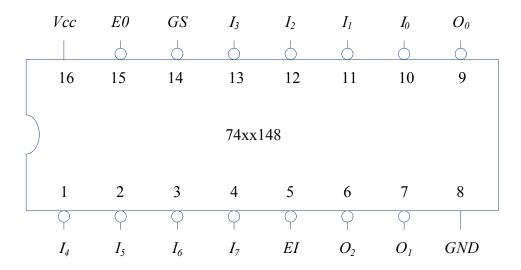

| 7.1 | Encoder                                      | 99  |

| 7.2 | Decoder                                      | 104 |

| 7.3 | Multiplexer                                  | 107 |

| 7.4 | De-multiplexer                               | 111 |

| 8   | Counters                                     | 114 |

| 8.1 | Asynchronous up-counter                      | 114 |

| 8.2 | Asynchronous down-counter                    | 117 |

| 8.3 | Asynchronous counters with incomplete cycles | 120 |

| 8.4 | Synchronous counters                         | 123 |

### Preface

The aim of this book is to provide readers with a fundamental understanding of digital system concepts such as logic gates for combinatorial logic circuit design and higher level logic elements such as counters and multiplexers.

First year undergraduates taking a course in computer science or engineering (and related disciplines like information technology) are the main target audience. Foundation year students and those taking pre-university courses (like '*A*' *levels*) will also benefit from the text.

I have tried to follow a simple approach in writing the text. Mathematics is used only where necessary. There are plenty of illustrations to aid the reader in understanding the concepts.

I hope I have done justice in discussing all the necessary fundamentals related to digital systems in this one volume. But by doing so, I had to skip advanced concepts such as computer hardware and programming and the interested reader can refer to advanced texts after mastering the basic concepts presented in this book.

For over a decade, I have greatly benefited from discussions with students and fellow colleagues who are too many to name here but have all helped in one way or another towards the contents of this book and I must thank them. I must also thank my wife for helping me prepare some of the contents. Many a time, she and my daughter had to put up with my absence to complete this book, so I dedicate this work to them. I am also indebted to Dr. Cota Navin Gupta for his useful comments in the early parts of the book. Finally, I trust that my proofreading is not perfect and some errors would remain in the text and I welcome any feedback or questions from the reader.

Ramaswamy Palaniappan July 2011

### About the author

Dr. Ramaswamy Palaniappan BE, MEngSc, PhD, SMIEEE, MIET, MBMES School of Computer Science and Electronic Engineering University of Essex, United Kingdom

Ramaswamy Palaniappan (better known as *Palani* among friends), received his first degree and MEngSc degree in electrical engineering and PhD degree in microelectronics/biomedical engineering in 1997, 1999 and 2002, respectively from University of Malaya, Kuala Lumpur, Malaysia. He is currently an academic with the School of Computer Science and Electronic Engineering, University of Essex, United Kingdom. Prior to this, he was the Associate Dean and Senior Lecturer at Multimedia University, Malaysia and Research Fellow in the Biomedical Engineering Research Centre-University of Washington Alliance, Nanyang Technological University, Singapore.

He has been teaching in a number of universities worldwide for the past 15 years in both computer science and engineering fields and has received numerous awards for excellence in teaching. He is an expert reviewer for many funding bodies such as Austria, Canada, EU, Russia and Malaysia. He founded and chaired the Bioinformatics division at the Centre for Bioinformatics and Biometrics in Multimedia University, Malaysia. His current research interests include biological signal processing, brain-computer interfaces, biometrics, artificial neural networks, genetic algorithms, and image processing. To date, he has published over 100 papers in peer-reviewed journals, book chapters, and conference proceedings.

Dr. Palaniappan is a senior member of the Institute of Electrical and Electronics Engineers and IEEE Engineering in Medicine and Biology Society, member in Institution of Engineering and Technology, and Biomedical Engineering Society. He also serves as editorial board member for several international journals. His pioneering studies on using brain signals for brain-computer interfaces and biometrics have received international recognition.

Ramaswamy Palaniappan July 2011

### 1 Number System Basics

Digital technology has become widespread and encompasses virtually all aspects of our everyday lives. We could see it being used in computers and related gadgets, entertainment, automation (robotics), medical etc. Though physical quantities measured in the real world are analogue, most of these are processed by digital means. In order to do this, we have to convert the measured analogue quantity into digital, process the digital quantity using digital circuitry and then reconvert to analogue.

The contents of this book concentrate on the digital circuit design to enable the processing of the digital quantity. But before we look into the principles of such designs, we need to understand the basics of number systems.

#### 1.1 Decimal Numbers

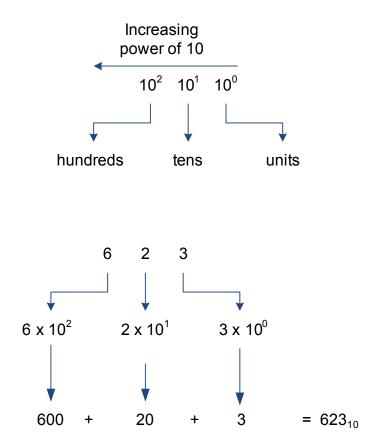

Decimal number system is the commonly used number system that has ten digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. It is also known as base (or radix) ten system since it has ten digits that can be used to represent any number. Figure 1.1 shows the positional values or weights of the decimal number system for an integer.

Figure 1.1: Decimal number system for integers.

The digit with least weight (i.e. the one on the foremost right) is known as the least significant digit (LSD) while the highest weight digit is known as the most significant digit (MSD). In the example shown in Figure 1.1, the MSD is digit 6 while the LSD is digit 3. Figure 1.2 shows the case for fractional decimal number.

Figure 1.2: Decimal number system for fractional numbers.

#### 1.2 Other Number Systems – Binary, Octal and Hexadecimal

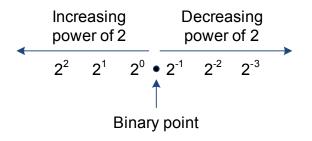

While decimal number system is the commonly used number system in everyday lives, digital devices uses only binary number system that consists of 0 and 1. The base is two for this system and Figure 1.3 show an example of binary number for decimal equivalent of  $6.25_{10}$

Figure 1.3: Binary number system with an example.

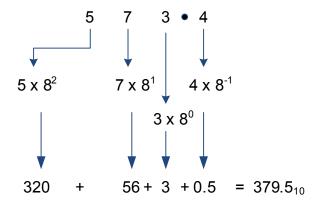

Similarly, octal and hexadecimal (hex in short) number systems have number bases of 8 and 16. For octal number system, the eight digits are 0, 1, 2, 3, 4, 5, 6, and 7 while hexadecimal number system has 16 digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, and F. Figure 1.4 gives examples on these number systems.

(a)

(b)

Figure 1.4: Number system examples (a) octal (b) hex.

12

#### 1.3 Conversion between different number systems

It is often necessary to convert a number from one base system to another. Converting a number to decimal is rather straightforward as we have seen in the previous examples. The weights or positional values (for the appropriate base) are multiplied with the digit and summed to give the decimal value. In this section, we will look at methods to convert numbers from decimal to binary, octal and hex. Other conversions such as octal to binary (and vice versa), binary to hex, hex to binary, octal to hex and hex to octal are also possible.

#### 1.3.1 Decimal to binary, octal and hex conversions

There are two methods that can be used to achieve decimal to binary conversion. The first method is by presenting the decimal value in units, tens, hundreds etc. For example:

$$2 6 = 16 + 8 + 2 = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 = 11010_{10}$$

The problem with this method is that certain positional values (such as  $2^2$  and  $2^0$  in the example above) can easily be forgotten. There is another method called repeated division that is more frequently employed. Figure 1.5 illustrates this method. It works by repeated division with a value of 2 (until the quotient is 0) and the remainder digits from each step represent the binary number (in reverse order).

| 24             |   |    | re            | mainder |     |  |

|----------------|---|----|---------------|---------|-----|--|

| 34<br>2        | = | 17 | $\rightarrow$ | 0       | LSD |  |

| <u>17</u><br>2 | = | 8  | ÷             | 1       |     |  |

| 8              | = | 4  | →             | 0       |     |  |

| 4              | = | 2  | ÷             | 0       |     |  |

| 2              | = | 1  | ÷             | 0       |     |  |

| 1<br>2         | = | 0  | <b>→</b>      | 1       | MSD |  |

**Figure 1.5:** Decimal to binary conversion example,  $34_{10} = 100010_2$ .

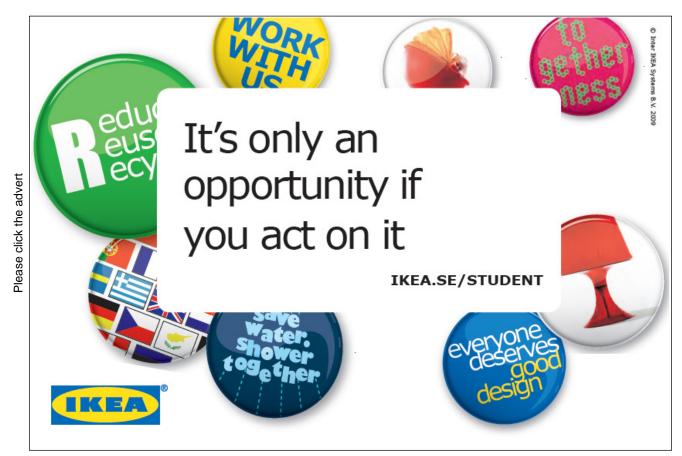

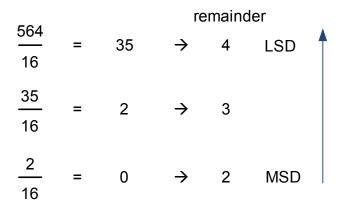

Similarly, we can convert a decimal number to octal and hex. Figures 1.6 and 1.7 illustrate the steps for these conversions. Do remember that the final answer is in the reverse order!

**Figure 1.6:** Decimal to octal conversion example,  $149_{10} = 225_8$ .

**Figure 1.7:** Decimal to hex conversion example,  $564_{10} = 234_{16}$ .

#### 1.3.2 Binary to Octal and vice versa

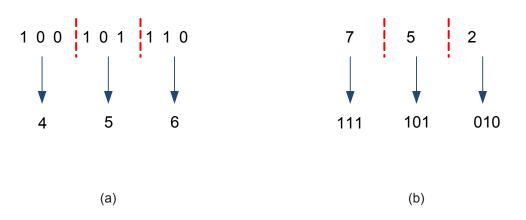

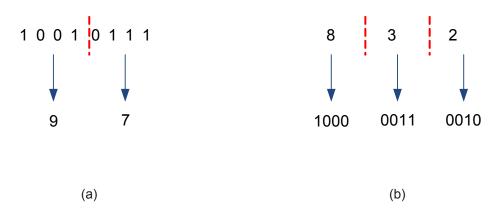

Any binary number can be converted to octal simply by grouping them in groups of three digits. For example,  $100101110_8$  can be converted to  $456_8$  as shown in Figure 1.8 (a). The reverse procedure of converting an octal number to binary can be done by writing three binary digit equivalent for each octal digit. This is shown in Figure 1.8 (b).

**Figure 1.8**: Octal to binary conversion example and vice versa: (a)  $100101110_2 = 456_8$  (b)  $752_8 = 111101010_2$ .

#### 1.3.3 Binary to Hex and vice versa

Similar to octal number, binary number can be converted to hex simply by grouping them in groups of four digits. For example,  $10010111_2$  can be converted to  $97_{16}$  as shown in Figure 1.9 (a). A hex number can be converted to binary by writing four binary digit equivalent for each hex digit. This is shown in Figure 1.9 (b).

**Figure 1.9:** Hex to binary conversion example and vice versa: (a)  $10010111_2 = 97_{16}$  (b)  $832_{16} = 100000110010_2$ .

#### 1.4 Other number codes

In this section, several other commonly used codes will be discussed.

#### 1.4.1 ASCII code

ASCII stands for American Standard Code for Information Interchange. Characters such as 'a', 'A', '@', '\$' each have a code that is recognised by the computer. Standard ASCII has 128 characters (represented by 7 binary digits; 2<sup>7</sup>=128), though the first 32 is no longer used. Extended ASCII has another 128 characters, mostly to represent special characters and mathematical symbols such as 'ÿ', 'ë', 'Σ', and 'σ'. Table 1.1 shows the standard ASCII code.

5C

5D

5E

5F

92

93

94

95

1011100

1011101

1011110

1011111

١

]

٨

108

109

110

111

6C

6D

6E

6F

| D'mal                                                                                                 | Hex                                                                                                   | B'ary                                                                                                                                                                                                                    | Char                                                     | D'mal                                                                   | Hex                                                                         | B'ary                                                        | Char                                              | D'mal                                                                       | Hex                                                             | B'ary                                                                                                   | Char                                                        |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 32                                                                                                    | 20                                                                                                    | 0100000                                                                                                                                                                                                                  | space                                                    | 48                                                                      | 30                                                                          | 0110000                                                      | 0                                                 | 64                                                                          | 40                                                              | 1000000                                                                                                 | @                                                           |

| 33                                                                                                    | 21                                                                                                    | 0100001                                                                                                                                                                                                                  | !                                                        | 49                                                                      | 31                                                                          | 0110001                                                      | 1                                                 | 65                                                                          | 41                                                              | 1000001                                                                                                 | А                                                           |

| 34                                                                                                    | 22                                                                                                    | 0100010                                                                                                                                                                                                                  | "                                                        | 50                                                                      | 32                                                                          | 0110010                                                      | 2                                                 | 66                                                                          | 42                                                              | 1000010                                                                                                 | В                                                           |

| 35                                                                                                    | 23                                                                                                    | 0100011                                                                                                                                                                                                                  | #                                                        | 51                                                                      | 33                                                                          | 0110011                                                      | 3                                                 | 67                                                                          | 43                                                              | 1000011                                                                                                 | С                                                           |

| 36                                                                                                    | 24                                                                                                    | 0100100                                                                                                                                                                                                                  | \$                                                       | 52                                                                      | 34                                                                          | 0110100                                                      | 4                                                 | 68                                                                          | 44                                                              | 1000100                                                                                                 | D                                                           |

| 37                                                                                                    | 25                                                                                                    | 0100101                                                                                                                                                                                                                  | %                                                        | 53                                                                      | 35                                                                          | 0110101                                                      | 5                                                 | 69                                                                          | 45                                                              | 1000101                                                                                                 | E                                                           |

| 38                                                                                                    | 26                                                                                                    | 0100110                                                                                                                                                                                                                  | &                                                        | 54                                                                      | 36                                                                          | 0110110                                                      | 6                                                 | 70                                                                          | 46                                                              | 1000110                                                                                                 | F                                                           |

| 39                                                                                                    | 27                                                                                                    | 0100111                                                                                                                                                                                                                  | 1                                                        | 55                                                                      | 37                                                                          | 0110111                                                      | 7                                                 | 71                                                                          | 47                                                              | 1000111                                                                                                 | G                                                           |

| 40                                                                                                    | 28                                                                                                    | 0101000                                                                                                                                                                                                                  | (                                                        | 56                                                                      | 38                                                                          | 0111000                                                      | 8                                                 | 72                                                                          | 48                                                              | 1001000                                                                                                 | н                                                           |

| 41                                                                                                    | 29                                                                                                    | 0101001                                                                                                                                                                                                                  | )                                                        | 57                                                                      | 39                                                                          | 0111001                                                      | 9                                                 | 73                                                                          | 49                                                              | 1001001                                                                                                 | I                                                           |

| 42                                                                                                    | 2A                                                                                                    | 0101010                                                                                                                                                                                                                  | *                                                        | 58                                                                      | 3A                                                                          | 0111010                                                      | :                                                 | 74                                                                          | 4A                                                              | 1001010                                                                                                 | J                                                           |

| 43                                                                                                    | 2B                                                                                                    | 0101011                                                                                                                                                                                                                  | +                                                        | 59                                                                      | 3B                                                                          | 0111011                                                      | ;                                                 | 75                                                                          | 4B                                                              | 1001011                                                                                                 | К                                                           |

| 44                                                                                                    | 2C                                                                                                    | 0101100                                                                                                                                                                                                                  | ,                                                        | 60                                                                      | 3C                                                                          | 0111100                                                      | <                                                 | 76                                                                          | 4C                                                              | 1001100                                                                                                 | L                                                           |

| 45                                                                                                    | 2D                                                                                                    | 0101101                                                                                                                                                                                                                  | -                                                        | 61                                                                      | 3D                                                                          | 0111101                                                      | =                                                 | 77                                                                          | 4D                                                              | 1001101                                                                                                 | м                                                           |

| 46                                                                                                    | 2E                                                                                                    | 0101110                                                                                                                                                                                                                  |                                                          | 62                                                                      | 3E                                                                          | 0111110                                                      | >                                                 | 78                                                                          | 4E                                                              | 1001110                                                                                                 | N                                                           |

| 47                                                                                                    | 2F                                                                                                    | 0101111                                                                                                                                                                                                                  | /                                                        | 63                                                                      | 3F                                                                          | 0111111                                                      | ?                                                 | 79                                                                          | 4F                                                              | 1001111                                                                                                 | 0                                                           |

|                                                                                                       |                                                                                                       |                                                                                                                                                                                                                          |                                                          |                                                                         |                                                                             |                                                              |                                                   | //                                                                          |                                                                 | 1001111                                                                                                 | U                                                           |

|                                                                                                       |                                                                                                       |                                                                                                                                                                                                                          |                                                          |                                                                         | 51                                                                          | UIIIII                                                       | :                                                 | ,,,                                                                         |                                                                 | 1001111                                                                                                 | 0                                                           |

| D'mal                                                                                                 | Hex                                                                                                   | B'ary                                                                                                                                                                                                                    | Char                                                     | D'mal                                                                   | Hex                                                                         | B'ary                                                        | :<br>Char                                         | D'mal                                                                       | Hex                                                             | B'ary                                                                                                   | Char                                                        |

| D'mal<br>80                                                                                           | Hex<br>50                                                                                             | B'ary<br>1010000                                                                                                                                                                                                         | Char<br>P                                                | ۱<br>i                                                                  |                                                                             |                                                              |                                                   |                                                                             | 1                                                               | 1                                                                                                       | 1                                                           |

|                                                                                                       |                                                                                                       | -                                                                                                                                                                                                                        |                                                          | D'mal                                                                   | Hex                                                                         | B'ary                                                        |                                                   | D'mal                                                                       | Hex                                                             | B'ary                                                                                                   | Char                                                        |

| 80                                                                                                    | 50                                                                                                    | 1010000                                                                                                                                                                                                                  | Р                                                        | D'mal<br>96                                                             | Hex<br>60                                                                   | B'ary<br>1100000                                             | Char                                              | D'mal<br>112                                                                | Hex<br>70                                                       | B'ary<br>1110000                                                                                        | Char<br>p                                                   |

| 80<br>81                                                                                              | 50<br>51                                                                                              | 1010000<br>1010001                                                                                                                                                                                                       | P<br>Q                                                   | D'mal<br>96<br>97                                                       | Hex<br>60<br>61                                                             | B'ary<br>1100000<br>1100001                                  | Char<br>`<br>a                                    | D'mal<br>112<br>113                                                         | Hex<br>70<br>71                                                 | B'ary<br>1110000<br>1110001                                                                             | Char<br>p<br>q                                              |

| 80<br>81<br>82                                                                                        | 50<br>51<br>52                                                                                        | 1010000<br>1010001<br>1010010                                                                                                                                                                                            | P<br>Q<br>R                                              | D'mal<br>96<br>97<br>98                                                 | Hex<br>60<br>61<br>62                                                       | B'ary<br>1100000<br>1100001<br>1100010                       | Char<br>`<br>a<br>b                               | D'mal<br>112<br>113<br>114                                                  | Hex<br>70<br>71<br>72                                           | B'ary<br>1110000<br>1110001<br>1110010                                                                  | Char<br>p<br>q<br>r                                         |

| 80<br>81<br>82<br>83                                                                                  | 50<br>51<br>52<br>53                                                                                  | 1010000<br>1010001<br>1010010<br>1010011                                                                                                                                                                                 | P<br>Q<br>R<br>S                                         | D'mal<br>96<br>97<br>98<br>99                                           | Hex<br>60<br>61<br>62<br>63                                                 | B'ary<br>1100000<br>1100001<br>1100010<br>1100011            | Char<br>`<br>a<br>b<br>c                          | D'mal<br>112<br>113<br>114<br>115                                           | Hex<br>70<br>71<br>72<br>73                                     | B'ary<br>1110000<br>1110001<br>1110010<br>1110011                                                       | Char<br>p<br>q<br>r<br>s                                    |

| 80<br>81<br>82<br>83<br>84                                                                            | 50<br>51<br>52<br>53<br>54                                                                            | 1010000<br>1010001<br>1010010<br>1010011<br>1010100                                                                                                                                                                      | P<br>Q<br>R<br>S<br>T                                    | D'mal<br>96<br>97<br>98<br>99<br>100                                    | Hex<br>60<br>61<br>62<br>63<br>64                                           | B'ary<br>1100000<br>1100001<br>1100010<br>1100011<br>1100100 | Char<br>`<br>a<br>b<br>c<br>d                     | D'mal<br>112<br>113<br>114<br>115<br>116                                    | Hex<br>70<br>71<br>72<br>73<br>74                               | B'ary<br>1110000<br>1110001<br>1110010<br>1110011<br>1110100                                            | Char<br>p<br>q<br>r<br>s<br>t                               |

| 80<br>81<br>82<br>83<br>84<br>85                                                                      | 50         51         52         53         54         55                                             | 1010000         1010001         1010010         1010011         1010100         1010101                                                                                                                                  | P<br>Q<br>R<br>S<br>T<br>U                               | D'mal<br>96<br>97<br>98<br>99<br>100<br>101                             | Hex<br>60<br>61<br>62<br>63<br>64<br>65                                     | B'ary<br>1100000<br>1100001<br>1100010<br>1100011<br>1100100 | Char<br>a<br>b<br>c<br>d<br>e                     | D'mal<br>112<br>113<br>114<br>115<br>116<br>117                             | Hex<br>70<br>71<br>72<br>73<br>74<br>75                         | B'ary<br>1110000<br>1110001<br>1110010<br>1110011<br>1110100<br>1110101                                 | Char<br>p<br>q<br>r<br>s<br>t<br>u                          |

| 80<br>81<br>82<br>83<br>84<br>85<br>86                                                                | 50         51         52         53         54         55         56                                  | 1010000         1010001         1010010         1010011         1010100         1010101         1010101         1010110                                                                                                  | P<br>Q<br>R<br>S<br>T<br>U<br>V                          | D'mal<br>96<br>97<br>98<br>99<br>100<br>101<br>102                      | Hex<br>60<br>61<br>62<br>63<br>64<br>65<br>66                               | B'ary<br>1100000<br>1100001<br>1100010<br>1100011<br>1100100 | Char<br>a<br>b<br>c<br>d<br>e<br>f                | D'mal<br>112<br>113<br>114<br>115<br>116<br>117<br>118                      | Hex<br>70<br>71<br>72<br>73<br>74<br>75<br>76                   | B'ary<br>1110000<br>1110001<br>1110010<br>1110011<br>1110100<br>1110101<br>1110110                      | Char<br>p<br>q<br>r<br>s<br>t<br>u<br>v                     |

| 80<br>81<br>82<br>83<br>84<br>85<br>86<br>87                                                          | 50         51         52         53         54         55         56         57                       | 1010000         1010001         1010010         1010011         1010100         1010101         1010110         1010111                                                                                                  | P<br>Q<br>R<br>S<br>T<br>U<br>V<br>V<br>W                | D'mal<br>96<br>97<br>98<br>99<br>100<br>101<br>102<br>103               | Hex<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>66<br>67                   | B'ary<br>1100000<br>1100001<br>1100010<br>1100011<br>1100100 | Char<br>a<br>b<br>c<br>d<br>e<br>f<br>g           | D'mal<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119               | Hex<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77             | B'ary<br>1110000<br>1110001<br>1110010<br>1110011<br>1110100<br>1110101<br>1110110                      | Char<br>p<br>q<br>r<br>s<br>t<br>u<br>v<br>v                |

| 80<br>81<br>82<br>83<br>84<br>85<br>86<br>87<br>88                                                    | 50         51         52         53         54         55         56         57         58            | 1010000         1010001         1010010         1010011         1010100         1010101         1010110         1010111         1010111         1010111                                                                  | P<br>Q<br>R<br>S<br>T<br>U<br>V<br>V<br>W<br>X           | D'mal<br>96<br>97<br>98<br>99<br>100<br>101<br>102<br>103<br>104        | Hex<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>66<br>67<br>68             | B'ary<br>1100000<br>1100001<br>1100010<br>1100011<br>1100100 | Char<br>a<br>b<br>c<br>d<br>e<br>f<br>g<br>h      | D'mal<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>120        | Hex<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78       | B'ary<br>1110000<br>1110001<br>1110010<br>1110011<br>1110100<br>1110101<br>1110110                      | Char<br>p<br>q<br>r<br>s<br>t<br>u<br>v<br>v<br>w<br>x      |

| 80         81         82         83         84         85         86         87         88         89 | 50         51         52         53         54         55         56         57         58         59 | 1010000         1010001         1010010         1010011         1010100         1010101         1010111         1010111         10100011         1010111         1010111         1010100         1010111         1011001 | P<br>Q<br>R<br>S<br>T<br>U<br>V<br>V<br>W<br>X<br>X<br>Y | D'mal<br>96<br>97<br>98<br>99<br>100<br>101<br>102<br>103<br>104<br>105 | Hex<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>65<br>66<br>67<br>68<br>69 | B'ary<br>1100000<br>1100001<br>1100010<br>1100011<br>1100100 | Char<br>a<br>b<br>c<br>d<br>e<br>f<br>g<br>h<br>i | D'mal<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>120<br>121 | Hex<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>79 | B'ary<br>1110000<br>1110001<br>1110010<br>1110011<br>1110100<br>1110101<br>1110111<br>111000<br>1111001 | Char<br>p<br>q<br>r<br>s<br>t<br>u<br>v<br>v<br>w<br>x<br>y |

#### Table 1.1: Standard ASCII code

1111100

1111101

1111110

1111111

I

}

~

1101100

1101101

1101110

1101111

I

m

n

о

124

125

126

127

7C

7D

7E

7F

#### 1.4.2 Binary coded decimal (BCD)

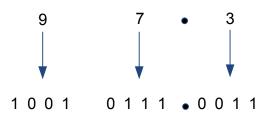

BCD is actually a set of binary numbers where a group of four binary numbers represent a decimal digit. As there are 10 basic digits in the decimal number system, four binary digits (bits) are required<sup>1</sup>. Figure 1.10 shows an example, while Table 1.2 gives the BCD code.

Figure 1.9: Hex to binary conversion example and vice versa: 973<sub>10</sub> = 10010111.0011<sub>BCD.</sub>

1 Three bits will only give eight representations, which is not enough for a decimal system.

Download free ebooks at bookboon.com

| Decimal | BCD  | Decimal | BCD  |

|---------|------|---------|------|

| 0       | 0000 | 5       | 0101 |

| 1       | 0001 | 6       | 0110 |

| 2       | 0010 | 7       | 0111 |

| 3       | 0011 | 8       | 1000 |

| 4       | 0100 | 9       | 1001 |

#### Table 1.2: BCD code

#### 1.4.3 Gray code

Gray code is another commonly encountered code system. The main feature of this code is that only one bit changes between two successive values. This system is less prone to errors and is considered very useful for practical applications such as mechanical switches and error correction in digital communication as compared to the standard binary system. Table 1.3 gives the BCD code with 4 bits (i.e. up to decimal value of 15).

| Decimal | Gray | Decimal | Gray |

|---------|------|---------|------|

| 0       | 0000 | 8       | 1100 |

| 1       | 0001 | 9       | 1101 |

| 2       | 0011 | 10      | 1111 |

| 3       | 0010 | 11      | 1110 |

| 4       | 0110 | 12      | 1010 |

| 5       | 0111 | 13      | 1011 |

| 6       | 0101 | 14      | 1001 |

| 7       | 0100 | 15      | 1000 |

#### Table 1.3: Gray code

## 2 Introduction to Logic Gates

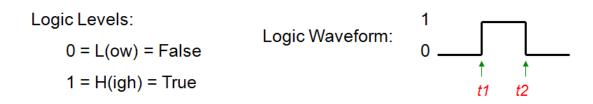

The basic building blocks for digital circuits are logic gates. Most logic gates are binary logic, i.e. have two states of 0 or 1. The input or output of these logic gates can only exist in one of these states, where a positive logic system treats 0 as FALSE value and 1 as TRUE value and conversely for the negative logic system. Figure 2.1 shows a logic waveform that is logic 1 between time t1 and t2 and is logic 0 at other times. Positive logic will be assumed throughout the book except where denoted otherwise.

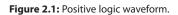

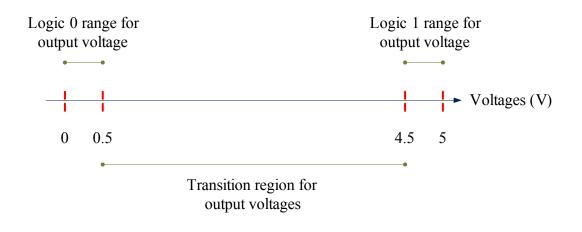

Figures 2.2 and 2.3 show the input and output voltage ranges for logic 0 and 1 for a common logic gate<sup>2</sup> used in digital devices. Transition region is the range where the voltage is not defined and hence, the input or output voltage from the device should not fall in this region as the logic value can be either 0 or 1. The output ranges are smaller as compared to input ranges, which is useful to reduce noise interference. The difference between the input-output ranges is known as noise margin. While it is usual to have a noise margin that is the same for both logical values, this does not have to be the case all the time.

To illustrate the usefulness of this noise margin, consider an example where there is noise interference in between two devices. Suppose the output voltage from the first digital device is 4.6 V (i.e. digital logic 1) and a spike (noise) of -0.5V enters as interference. The value of input voltage to the second device will be 4.1 V and the input digital level will still be 1. Without this noise margin, the digital level input to the second device will be unpredictable as it will fall within the transition region. The difference between input and output ranges for a given logic value is known as guaranteed noise immunity, which is 1 V in this case. It should also be obvious that the transition region for output voltage will be wider than for the input voltage because of this noise margin.

<sup>2</sup> The gate is actually a CMOS type NAND gate. NAND gates will be discussed later in the chapter.

Figure 2.2: Input logic related to actual voltages.

3

Figure 2.3: Output logic related to actual voltages.

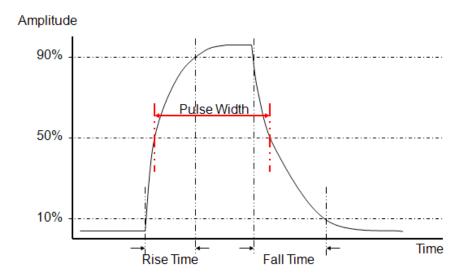

Actual pulse waveform does not resemble the form shown in Figure 2.1, but is rather like the one shown in Figure  $2.4^3$  where there is a period of time required for the pulse to rise and fall and these are known as rise and fall times, respectively. The time taken for the pulse to rise from 10% to 90% of the amplitude is rise time while the fall time is the time taken for the amplitude value to drop to 10% from 90%. The actual rise and fall times for a digital device depends on its specifications; costly devices have smaller times. The pulse width is measured using 50% of the rise and fall amplitude values as shown in the figure.

Figure 2.4: An example of actual pulse waveform.

Even this figure is simplified for ease of understanding. Actual waveform will have lots of spikes.

#### 2.1 AND gate

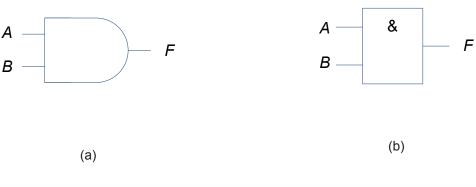

Basically AND gate is composed of two inputs and a single output as shown in Figure 2.5 with algebraic representation<sup>4</sup>  $F = A \cdot B$  or simply . F = AB The traditional symbol shown in Figure 2.5(a) is more commonly employed in text books. However, the IEEE/ANSI symbol as shown in Figure 2.5(b) is gaining popularity and has the advantage of containing qualifying symbols inside the logic-symbol that describes the operation of the gate. The truth table that gives the output *F* for inputs *A* and *B* is given in Table 2.1. It can be seen that the output is LOW (FALSE) when any one of the inputs is LOW (FALSE) and the output is only HIGH (TRUE) when all the inputs are HIGH (TRUE).

Figure 2.5: AND gate logic symbols (a) traditional (b) IEEE/ANSI standard.

| А | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

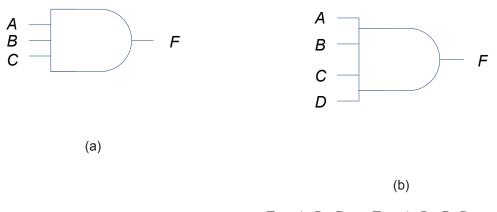

AND gate inputs do not have to be limited to two; there can be any number of inputs greater than one as shown in Figure 2.6.

<sup>4</sup> Also known as Boolean or logic expression.

Figure 2.6: Three and four input AND gates: (a)  $F = A \cdot B \cdot C$  (b)  $F = A \cdot B \cdot C \cdot D$ .

#### 2.1.1 Timing diagram

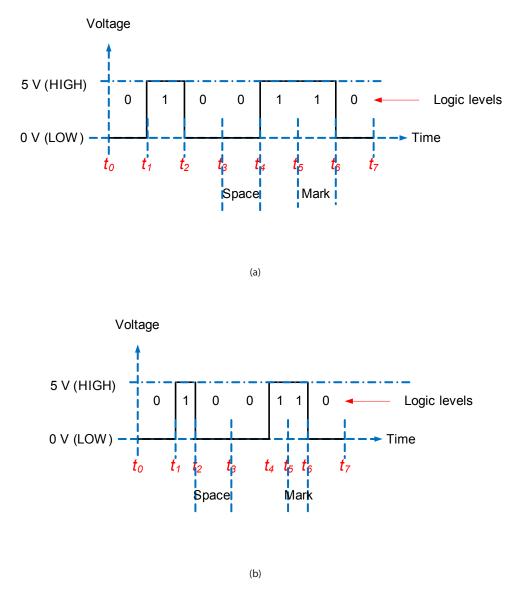

Timing diagram is useful in describing the relationship between the inputs and output of a logic gate. The inputs of a digital logic gate can be shown diagrammatically as a waveform that represents the changing values over time. A waveform corresponding to the changing values of the inputs over time will be generated at the output of the logic gate. Figure 2.7 show examples of timing diagram waveform for equal and unequal mark-space cycles. The mark represents the time for logic level HIGH, while the space represents the time for logic level LOW. Equal mark-space requires periodic clock pulse<sup>5</sup>. All the discussion in this book will be using equal mark-space timing waveforms only.

5 Clock pulses will be discussed in later chapters.

# With us you can shape the future. Every single day.

For more information go to: www.eon-career.com

Your energy shapes the future.

Figure 2.7: Example of timing diagram waveforms: (a) equal mark-space (b) unequal mark-space.

#### 2.1.2 Timing diagram example for AND gate

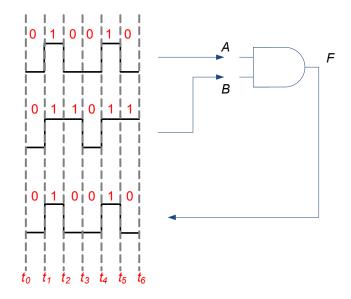

Figure 2.8 shows an example of a timing diagram for a two-input AND gate. At each time block, the inputs *A* and *B* affect the output *F*. For example, in time block  $t_0$  to  $t_1$ , both inputs are LOW, so the output is also LOW. Similarly, the entire timing waveform for the output can be obtained using AND operation of inputs in each time block.

Figure 2.8: Timing diagram waveform for a two-input AND gate.

#### 2.2 OR gate

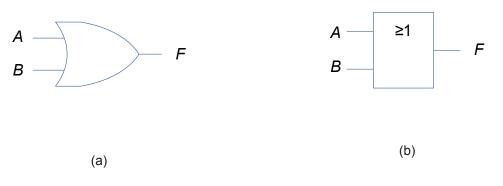

OR gate as shown in Figure 2.9 has algebraic representation, F = A + B. The truth table that gives the output *F* for inputs *A* and *B* is given in Table 2.2. It can be seen that the output is HIGH when any one of the inputs is HIGH and the output is only LOW when all the inputs are LOW.

Figure 2.9: OR gate logic symbols: (a) traditional (b) IEEE/ANSI standard.

#### Table 2.2: Truth table for two-input OR gate

| А | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Similar to AND gate, there can be any number of inputs greater than one as shown in Figure 2.10.

Figure 2.10: Three and four input OR gates: (a) Y = A + B + C (b) Y = A + B + C + D.

#### 2.2.1 Timing diagram example for OR gate

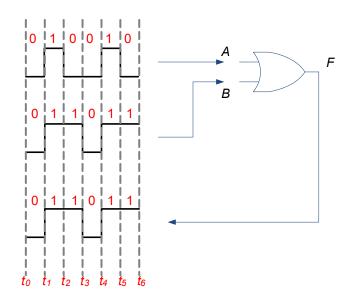

Figure 2.11 shows an example of a timing diagram for a two-input OR gate. At each time block, the inputs A and B affect the output F. For example, in time block  $t_5$  to  $t_6$ , one input is HIGH, so the output is HIGH. Similarly, the entire timing waveform for the output can be obtained using OR operation of inputs in each time block.

Figure 2.11: Timing diagram waveform for a two-input OR gate.

#### NOT gate 2.3

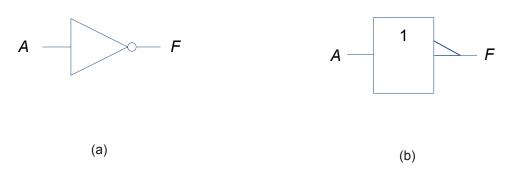

NOT gate is also known as INVERTER as it inverts (complements) the input logic level. It is shown in Figure 2.12 and has only one input and one output with algebraic representation of  $F = \overline{A}$  or F = A'. The bubble in the symbol denotes inversion (without it, the symbol will represent a buffer gate that does not alter the logic level; in IEEE/ANSI standard, the bubble is replaced by a triangle). The truth table for NOT gate is given in Table 2.3.

Figure 2.12: NOT gate logic symbols: (a) traditional (b) IEEE/ANSI standard.

Table 2.3: Truth table for NOT gate

| Α | F |

|---|---|

| 0 | 1 |

| 1 | 0 |

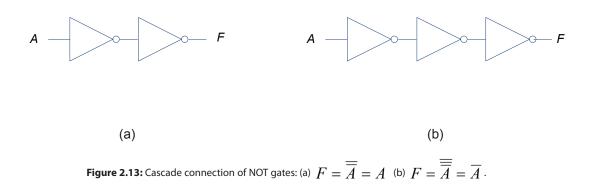

NOT gate can also be connected in cascade and a few examples are shown in Figure 2.13. It should be obvious that odd number of NOT gate connections give output logic level that is complement to the input logic level and an even number of NOT gates connections give output logic level that is the same as the input logic level.

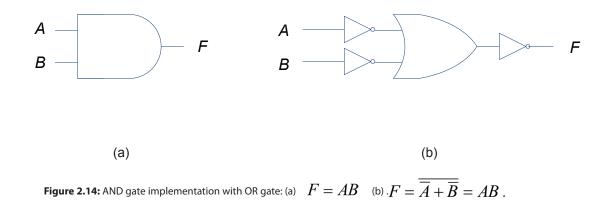

#### 2.4 AND implementation with OR gate and vice versa

It is useful to know that AND gate logic can be easily implemented using OR gate and vice versa through a simple process using additional NOT gates. For example, an AND gate equivalent can be constructed with an OR gate with both the inputs and outputs inverted through NOT gates. Figure 2.14 shows an example with equivalent truth table in Table 2.4. This is actually DeMorgan's first theorem, which will be discussed in detail in Chapter Three. It is mentioned here so that the reader is aware that it is possible to implement one gate logic with another gate(s).

|   |                  |   | $\overline{A}$ | $\overline{B}$ | $F = \overline{A} + \overline{B}$ | $F = \overline{\overline{A} + \overline{B}}$ |

|---|------------------|---|----------------|----------------|-----------------------------------|----------------------------------------------|

| 0 | 0<br>1<br>0<br>1 | 0 | 1              | 1              | 1                                 | 0                                            |

| 0 | 1                | 0 | 1              | 0              | 1                                 | 0                                            |

| 1 | 0                | 0 | 0              | 1              | 1                                 | 0                                            |

| 1 | 1                | 1 | 0              | 0              | 0                                 | 1                                            |

Table 2.4: Truth table illustrating AND gate implementation using OR and NOT gates

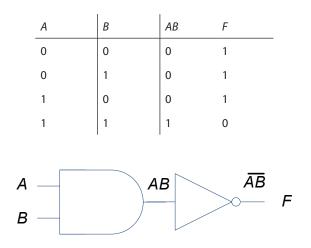

#### 2.5 NAND gate

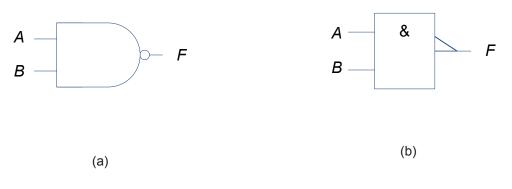

NAND and NOR gates that will be discussed in the following section are known as universal gates as combinations of these gates are sufficient to obtain equivalent operation of OR, AND or NOT gates. However, this is different to the implementation discussed in Section 2.4 as either NAND or NOR gates on their own will be sufficient to implement logic function of any of the other gates. NAND gate logic symbol is shown in Figure 2.15 (note the addition of a bubble when compared to AND gate) and its truth table is shown in Table 2.5. A NAND gate operation can also be obtained through cascade operation of AND and NOT gates as shown in Figure 2.16. Algebraically, the operation can be defined as  $F = \overline{AB}$ .

Figure 2.15: NAND gate logic symbols: (a) traditional (b) IEEE/ANSI standard.

Table 2.5: Truth table for NAND gate

Figure 2.16: NAND gate logic using AND and NOT gates.

Figure 2.17 shows an example for implementing an AND gate using NAND gates only. The blue shaded tiny bubble represents branch-off of the signal and should not be confused with the *empty* bubble that is used to represent inversion operation. Similarly, other gates such as OR and NOT can be implemented using NAND gates and these are left as exercises for the reader.

Figure 2.17: AND gate implementation using two NAND gates.

Download free ebooks at bookboon.com

30

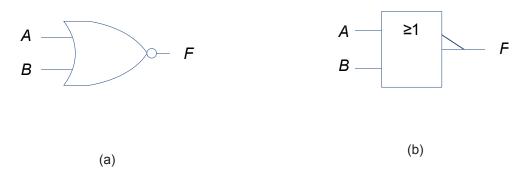

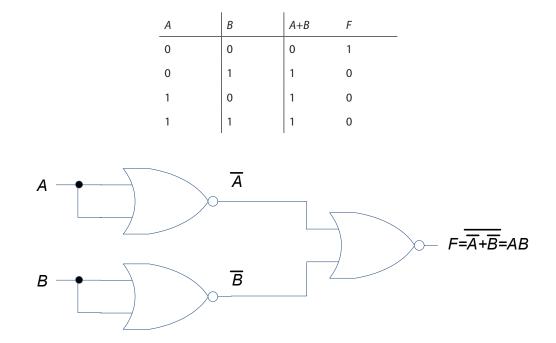

#### 2.6 NOR gate

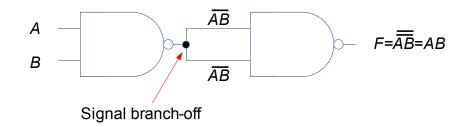

NOR gate is basically an OR gate with the output inverted. Figure 2.18 shows the logic symbol with truth table shown in Table 2.6. Algebraically, the operation can be defined as  $F = \overline{A + B}$ . Similar to NAND gate, several NOR gates can be used to implement AND, OR or NOT gates. An example of this is shown in Figure 2.19 and the reader can easily verify through the use of truth tables that F = AB.

Figure 2.18: NOR gate logic symbols: (a) traditional (b) IEEE/ANSI standard.

Table 2.6: Truth table for NOR gate

Figure 2.19: AND gate logic implementation using NOR gates.

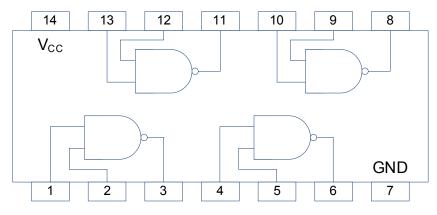

#### 2.7 Integrated circuits

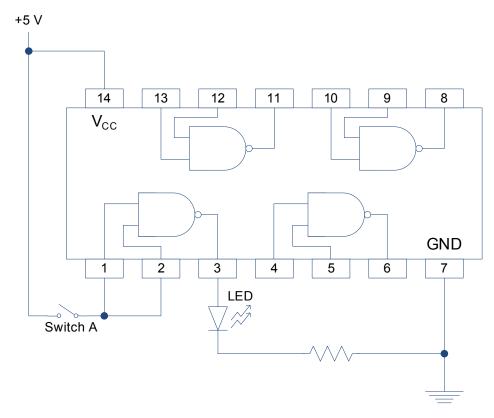

All the gates that we have discussed in this chapter are manufactured as integrated circuit (IC) with several gates in one IC. For example, 74LS00 is a transistor-transistor logic (TTL) technology based IC that has four (quad) two-input NAND gates. Complementary Metal-Oxide Semiconductor (CMOS) is another technology that is widely used for manufacturing IC but TTL devices are more commonly employed for laboratory experiments as they are more robust to electrostatic noise. Figure 2.20 shows the pin configuration of 74LS00 and Figure 2.21 shows an example of pin configurations to implement NOT operation. Pin 14 is connected to the power supply while pin 7 is the ground pin. It should be obvious that the LED will only light-up (i.e. the output will be HIGH) if switch A is turned OFF (i.e. made to logic level LOW) – similar to the input and output values as in the truth table shown in Table 2.3.

Figure 2.20: 74LS00 - Quad NAND IC.

Figure 2.21: NOT gate implementation example using 74LS00.

## 3 Combinatorial Logic Circuits

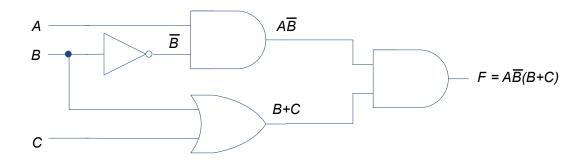

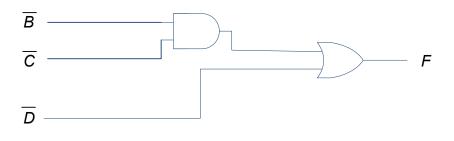

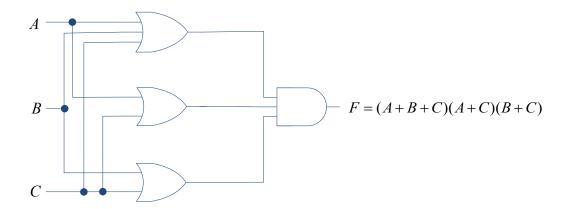

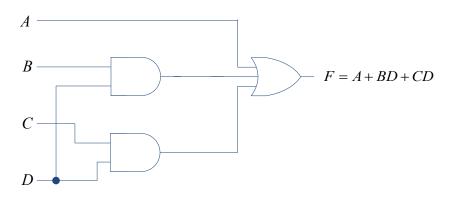

In the previous chapter, operation and truth tables of single gates were discussed. However, in practise, single gates are seldom useful and combinations of several gates are employed for a particular application. For example, see Figure 3.1 where different gates are used to obtain the output F.

Figure 3.1: Example of combinatorial logic circuit.

### Brain power By 2020, wind could provide one-tenth of our planet's electricity needs. Already today, SKF's innovative knowhow is crucial to running a large proportion of the world's wind turbines. Up to 25 % of the generating costs relate to maintenance. These can be reduced dramatically thanks to our stems for on-line condition monitoring and automatic lubrication. We help make it more economical to create cleaner, cheaper energy out of thin air. By sharing our experience, expertise, and creativity, industries can boost performance beyond expectations. Therefore we need the best employees who can neet this challenge! The Power of Knowledge Engineering Plug into The Power of Knowledge Engineering. Visit us at www.skf.com/knowledge

#### 3.1 Logic circuit simplification

Very often, there is the need to simplify logic circuits (whenever possible). For example, the circuit shown in Figure 3.1 requires four gates but equivalent logic output can be obtained with just two gates by simplifying the expression as follows:

$$F = A\overline{B}(B+C)$$

=  $A\overline{B}B + A\overline{B}C$  after expanding

=  $A\overline{B}C$ .

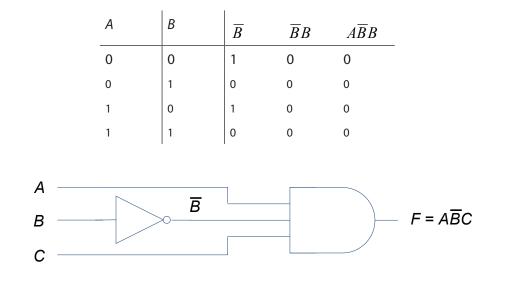

$A\overline{B}B$  is zero due to the presence of  $\overline{B}B$  as shown in the truth table given in Table 3.1. The simplified circuit is given in Figure 3.2. Table 3.2 gives the truth table and it can be seen that the outputs given by expressions  $F = A\overline{B}(B+C)$  and  $F = A\overline{B}C$  are the same.

**Table 3.1:** Truth table for  $A\overline{B}B$

Figure 3.2: Simplified logic circuit.

| A | В | С | $F = A\overline{B}(B+C)$ | $F = A\overline{B}C$ |

|---|---|---|--------------------------|----------------------|

| 0 | 0 | 0 | 0                        | 0                    |

| 0 | 0 | 1 | 0                        | 0                    |

| 0 | 1 | 0 | 0                        | 0                    |

| 0 | 1 | 1 | 0                        | 0                    |

| 1 | 0 | 0 | 0                        | 0                    |

| 1 | 0 | 1 | 1                        | 1                    |

| 1 | 1 | 0 | 0                        | 0                    |

| 1 | 1 | 1 | 0                        | 0                    |

**Table 3.2:** Truth table for  $F = A\overline{B}(B+C)$  and  $F = A\overline{B}C$

The above simplification may not be clear at this stage but that will be the purpose of the following sections to look into Boolean algebra that will be useful to simplify logic circuits. Not only will the simplification result in lower cost, smaller and simpler design (since fewer gates will be used), it will also reduce other complications such as overheating and propagation delay.

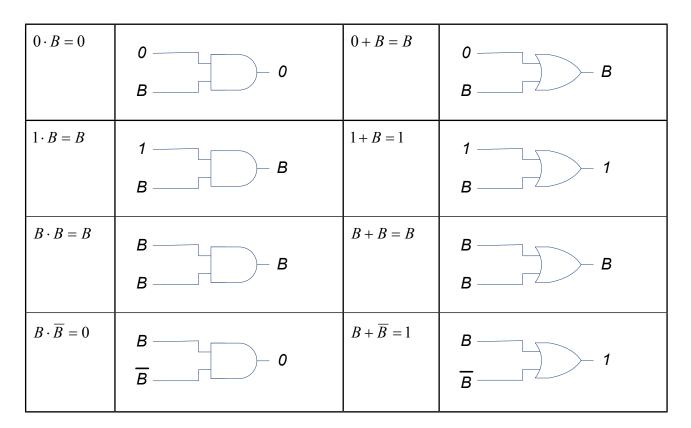

#### 3.2 Boolean algebra

Basic axioms of Boolean algebra are shown in Table 3.3, while Table 3.4 shows the Boolean theorems for operation of a single variable and a constant (either 0 or1).

Boolean algebra satisfies commutative and associative laws. Therefore, the order of variables in a product or sum does not matter and the order of evaluating sub-expression in brackets does not matter. For example:

Commutative law: A + B = B + A and  $A \cdot B = B \cdot A$ ;

Associative law: A + (B + C) = (A + B) + C = A + B + C and  $A \cdot (B \cdot C) = (A \cdot B) \cdot C = A \cdot B \cdot C$ .

Boolean algebra also satisfies the distributive law where the expression can be expanded by multiplying out the terms. For example:

Distributive law:  $A \cdot (B + C) = A \cdot B + A \cdot C$ .

It should be evident by now that when an expression contains AND and OR, AND operator takes precedence over OR operator. For example,  $0 \cdot 1 + 1 \cdot 1 = 0 + 1 = 1$  and not  $0 \cdot 1 + 1 \cdot 1 = 0 \cdot 1 \cdot 1 = 0$ .

| $\overline{1} = 0$ | 7 0         | $\overline{0} = 1$ | 0 1         |

|--------------------|-------------|--------------------|-------------|

| 1.1=1              |             | $0 \cdot 0 = 0$    |             |

| $0 \cdot 1 = 0$    | 0<br>1<br>1 | $1 \cdot 0 = 0$    |             |

| 0+1=1              |             | 1+0=1              |             |

| 1+1=1              |             | 0+0=0              | 0<br>0<br>0 |

#### Table 3.3: Basic axioms of Boolean algebra

#### Table 3.4: Boolean theorems for operation of a single variable and a constant

### Are you considering a European business degree? X Copenhagen Business School LEARN BUSINESS at university level. MEET a culture of new foods, music We mix cases with cutting edge ENGAGE in extra-curricular activities and traditions and a new way of research working individually or in such as case competitions, sports, studying business in a safe, clean teams and everyone speaks English. etc. - make new friends among CBS' environment - in the middle of Bring back valuable knowledge and 18,000 students from more than 80 Copenhagen, Denmark. experience to boost your career. countries. EFMD CEMS PIM Association of MBAs EQUIS See what we look like and how we work on cbs.dk

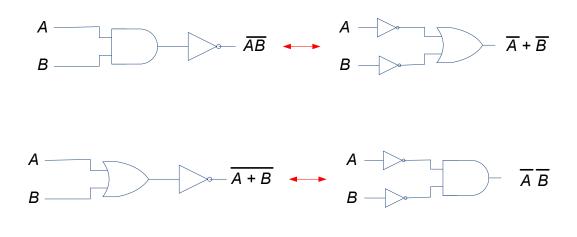

# 3.3 DeMorgan's theorem

DeMorgan's theorem is very useful to simplify expressions when they contain a bar (inversion) over more than a single variable. It states that an inverted expression can be replaced by its individual inverted variables but with AND replaced by OR and vice versa. For example:

DeMorgan's theorem:  $\overline{A \cdot B} = \overline{A} + \overline{B}$  and  $\overline{A + B} = \overline{A} \cdot \overline{B}$

Figure 3.3 shows the circuit equivalence using DeMorgan's theorem.

Figure 3.3: Circuit equivalence using DeMorgan's theorem.

# 3.3.1 Examples illustrating DeMorgan's theorem

The following examples show the usefulness of using DeMorgan's theorem. Note that from now on, the use of AND ( $\cdot$ ) sign in the expression will be dropped for simplicity sake unless noted otherwise, so  $F = A \cdot B \cdot C$  will be written as F = ABC.

| $F = \overline{A + B + \overline{C}}$ $= \overline{A}\overline{B}\overline{\overline{C}}$ $= \overline{A}\overline{B}C.$    | apply DeMorgan's theorem                                   |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| $F = \overline{ABC + D}$<br>= $\overline{ABC}\overline{D}$<br>= $\overline{D}(\overline{A} + \overline{B} + \overline{C}).$ | apply DeMorgan's theorem<br>apply DeMorgan's theorem again |

| $F = A + \overline{(B+C)D}$ $= A + \overline{B+C} + \overline{D}$ $= A + \overline{B}\overline{C} + \overline{D}.$          | apply DeMorgan's theorem<br>apply DeMorgan's theorem again |

# 3.4 More examples

In this section, several examples are given to illustrate simplification using Boolean algebra and DeMorgan's theorem:

| $F = \overline{A + B} + \overline{A}B$    | apply DeMorgan's theorem                |

|-------------------------------------------|-----------------------------------------|

| $=\overline{A}\overline{B}+\overline{A}B$ |                                         |

| $=\overline{A}(\overline{B}+B)$           | see Table 3.4, $(\overline{B} + B) = 1$ |

| $=\overline{A}$                           |                                         |

| $F = \overline{A + B + C} + A\overline{B} + \overline{B}C$   | apply DeMorgan's theorem                                        |

|--------------------------------------------------------------|-----------------------------------------------------------------|

| $= \overline{A}\overline{B}\overline{C} + \overline{B}(A+C)$ |                                                                 |

| $=\overline{B}(\overline{A}\overline{C}+A+C)$                |                                                                 |

| $=\overline{B}(\overline{A+C}+A+C)$                          | apply inverse of DeMorgan's theorem                             |

| $=\overline{B}$ .                                            | see Table 3.4, since $(\overline{X} + X) = 1$ where $X = A + C$ |

$$F = \overline{AB} + ABC$$

apply DeMorgan's theorem<sup>6</sup>

$$= \overline{A} + \overline{B} + ABC$$

$$= \overline{A} + \overline{B} + C(AB)$$

$$= \overline{A} + \overline{B} + C(\overline{AB})$$

apply DeMorgan's theorem again

$$= \overline{A} + \overline{B} + C(\overline{\overline{A} + \overline{B}})$$

let  $X = \overline{A} + \overline{B}$

$$= X + C\overline{X}$$

$$= X + C\overline{X} + XC$$

add  $XC$  since  $X + XC = X(1 + C) = X$

$$= X + C(\overline{X} + X)$$

$$= X + C$$

as  $X + \overline{X} = 1$

$$= \overline{A} + \overline{B} + C$$

replace  $X = \overline{A} + \overline{B}$

6 There is a simpler method to obtain the solution by letting X=AB in the first place but the shown procedure illustrates several useful simplifications.

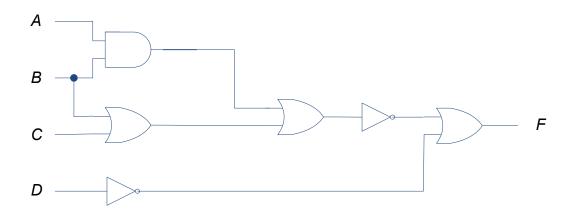

# As another example, consider the circuit diagram given in Figure 3.4 which can be simplified as

Figure 3.4: Logic circuit example for simplification.

| $\overline{AB + (B + C)} + \overline{D}$                                                     | obtain the expression                                  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------|

| $\overline{AB}(\overline{B+C}) + \overline{D}$                                               | using DeMorgan's theorem on the top (outermost) invers |

| $(\overline{A} + \overline{B})(\overline{B}\overline{C}) + \overline{D}$                     | using DeMorgan's theorem again                         |

| $\overline{A}\overline{B}\overline{C} + \overline{B}\overline{B}\overline{C} + \overline{D}$ | after expanding                                        |

| $\overline{A}\overline{B}\overline{C} + \overline{B}\overline{C} + \overline{D}$             | since $\overline{B}\overline{B} = \overline{B}$        |

| $\overline{B}\overline{C}(\overline{A}+1)+\overline{D}$                                      | as $\overline{A} + 1 = 1$                              |

| $\overline{B}\overline{C} + \overline{D}$ .                                                  |                                                        |

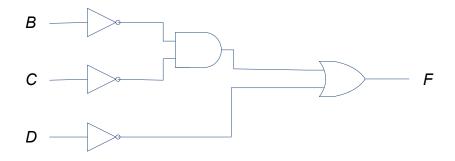

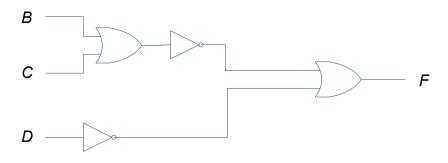

The correctness of the simplified expression can be verified by constructing a truth table and comparing the output from both expressions. The simplified logic circuit diagram is shown in Figure 3.5 where only five gates are required as opposed to six gates in the original circuit. It can be seen that there is no input A as its logic value does not affect the output based on the simplified expression.

Figure 3.5: Simplified logic circuit of the example shown in Figure 3.4.

While the expression for the logic circuit shown in Figure 3.5 is simplified to single literals, it is interesting to note that another equivalent logic circuit shown in Figure 3.6 only requires four gates as  $F = \overline{B}\overline{C} + \overline{D} = \overline{B+C} + \overline{D}$ .

Figure 3.6: Equivalent logic circuit of the example shown in Figures 3.4 and 3.5.

If complement inputs are available, then the simplified circuit shown in Figure 3.5 will only require two gates as shown in Figure 3.7.

Figure 3.7: Simplified logic circuit when complement inputs are available.

#### 3.5 XOR and XNOR gates

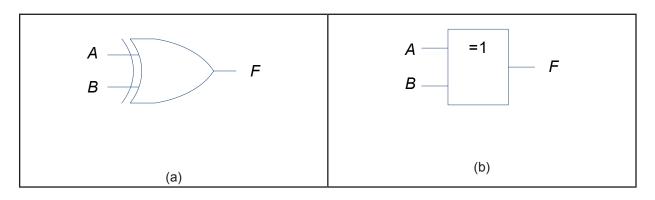

To conclude the chapter, it is useful to look at two more frequently used gates: Exclusive OR (XOR) and Exclusive NOR (XNOR). These gates would be useful when circuitry such as half adders and full adders are discussed in later chapters. XOR gate as shown in Figure 3.8 has algebraic representation,  $F = A\overline{B} + \overline{A}B$  or more commonly written as  $F = A \oplus B$ .

The truth table that gives the output F for inputs A and B is given in Table 3.5. It can be seen that when both inputs have the same logic value, the output is LOW. The output is HIGH when the input logic values are dissimilar, i.e. one LOW and one HIGH.

Figure 3.8: NOR gate logic symbols: (a) traditional (b) IEEE/ANSI standard.

#### Table 3.5: Truth table for two-input XOR gate

| A | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

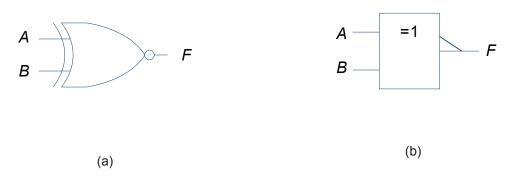

XNOR gate is simply XOR with an inversion. The gate is shown in Figure 3.9 and has algebraic representation,

| $F = \overline{A\overline{B} + \overline{A}B}$                      |                                               |

|---------------------------------------------------------------------|-----------------------------------------------|

| $F = \overline{A\overline{B}}\overline{\overline{A}B}$              | using DeMorgan's theorem on the top inversion |

| $F = (\overline{A} + B)(A + \overline{B})$                          | using DeMorgan's theorem again                |

| $F = \overline{A}A + B\overline{B} + AB + \overline{A}\overline{B}$ | after expanding                               |

| $F = AB + \overline{A}\overline{B}$                                 | expression for XNOR                           |

or more commonly written as  $F = \overline{A \oplus B}$ .

The truth table is given in Table 3.6. The output is HIGH when both inputs have the same logic value. The output is LOW when the input logic values are dissimilar, i.e. one LOW and one HIGH.

Figure 3.9: XNOR gate logic symbols: (a) traditional (b) IEEE/ANSI standard.

#### Table 3.6: Truth table for two-input XNOR gate

| А | В | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

# 3.5.1 Boolean algebra for XOR operation

Table 3.7 shows the Boolean algebra for XOR operation. XOR operation is also both commutative and associative:  $A \oplus B = B \oplus A$  and  $A \oplus (B \oplus C) = (A \oplus B) \oplus C = A \oplus B \oplus C$ .

| $A \oplus 0 = A$            | $A \oplus A = 0$            | $A \oplus \overline{B} = \overline{A \oplus B}$ |

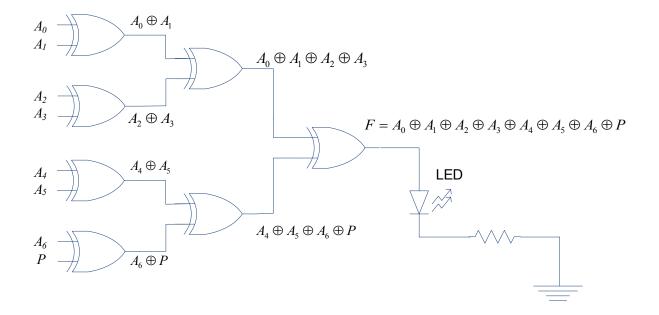

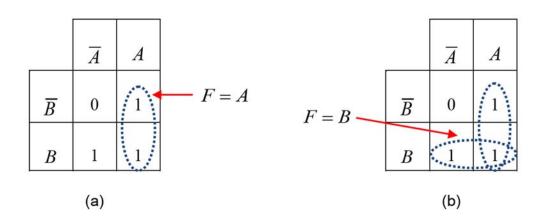

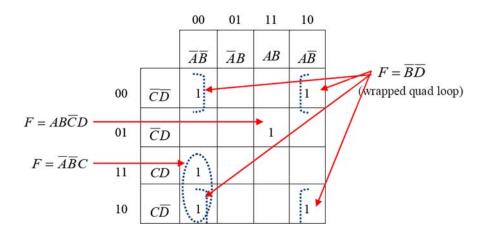

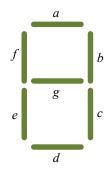

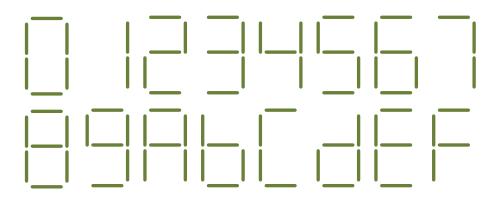

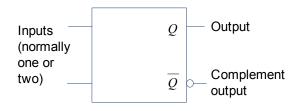

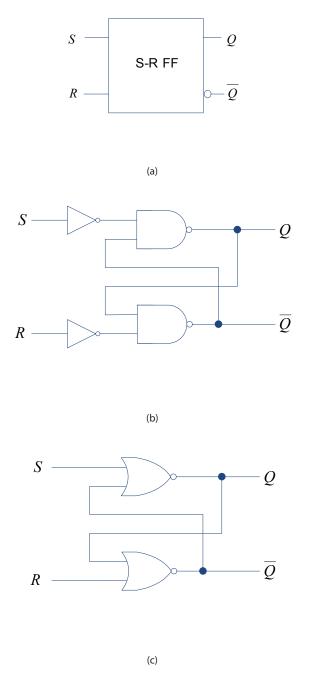

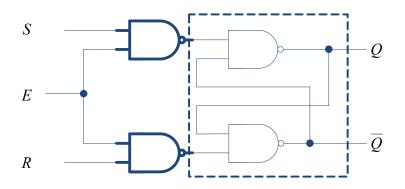

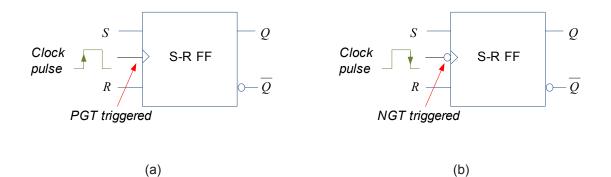

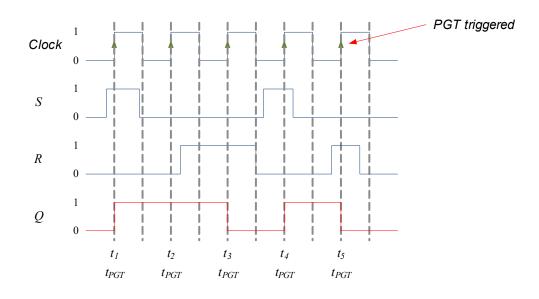

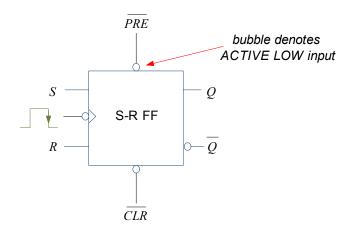

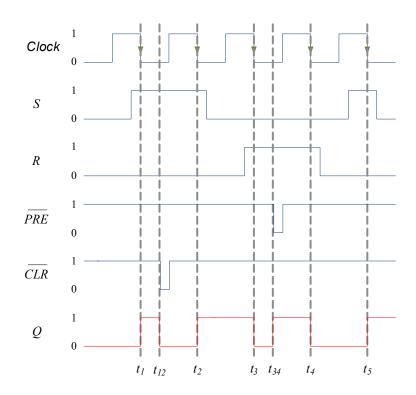

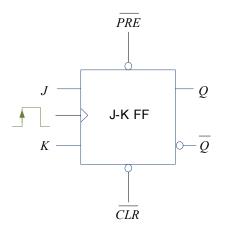

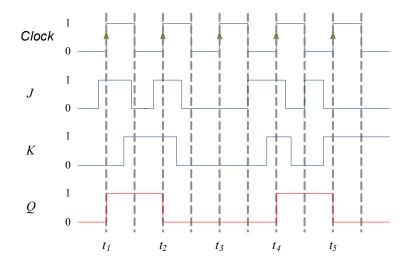

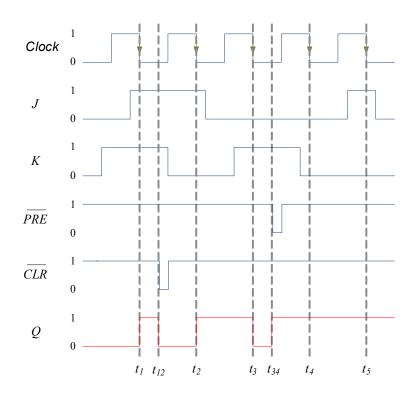

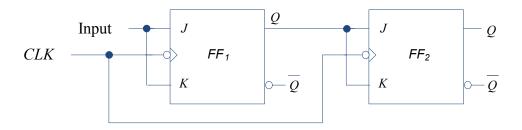

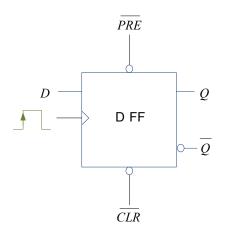

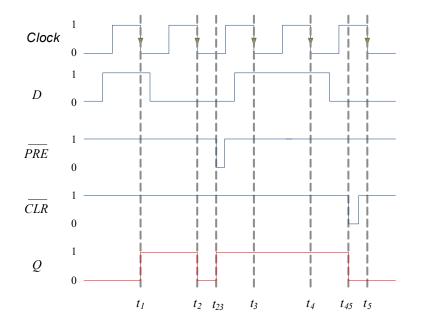

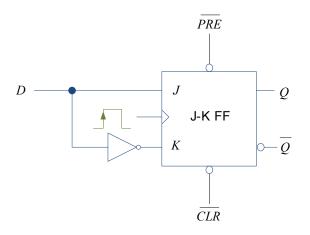

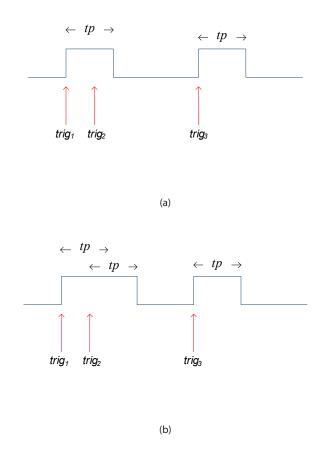

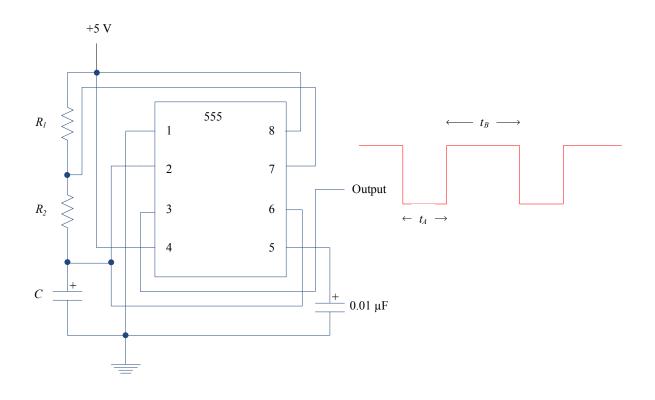

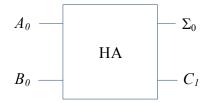

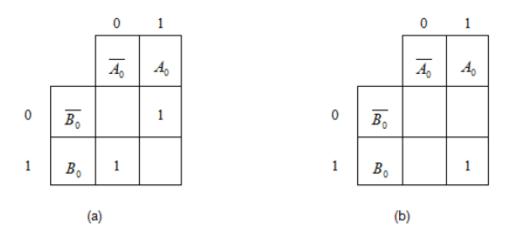

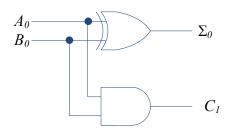

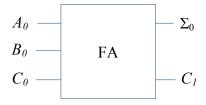

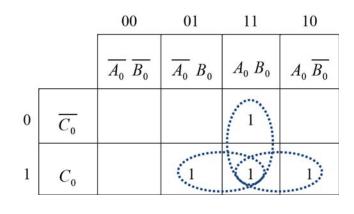

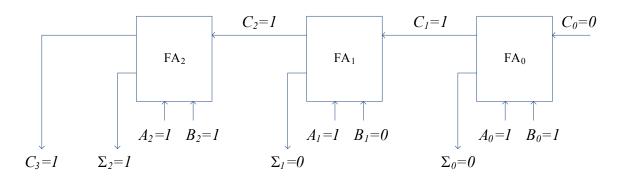

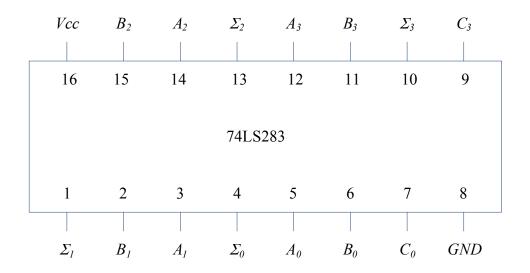

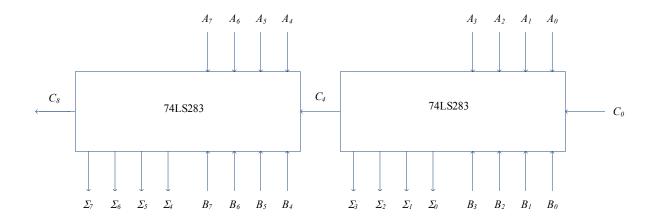

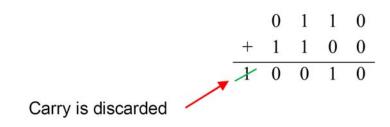

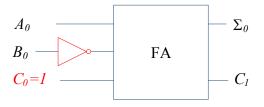

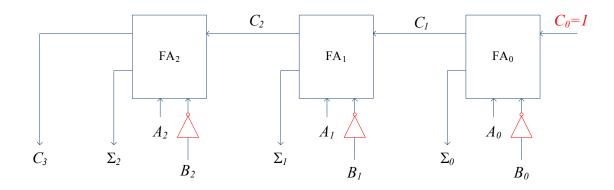

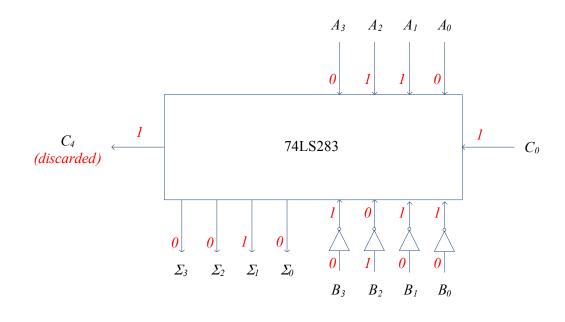

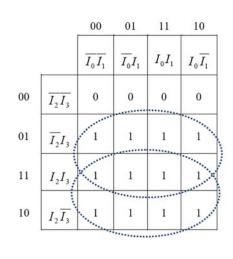

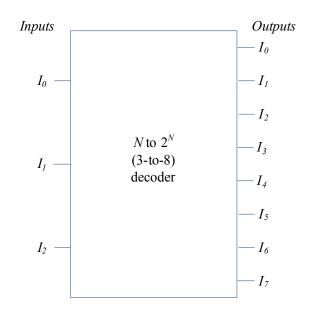

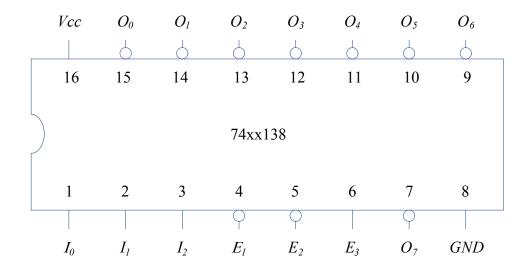

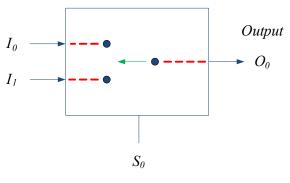

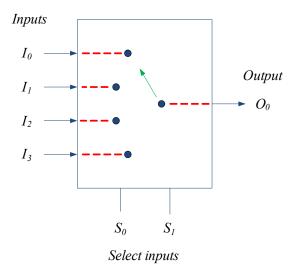

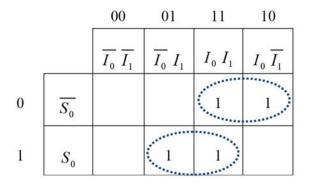

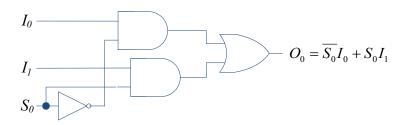

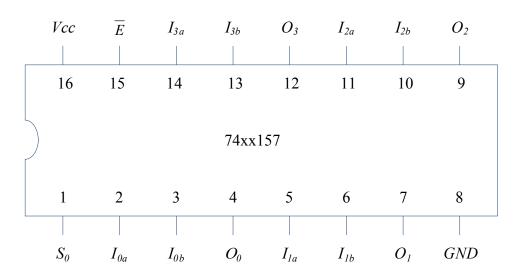

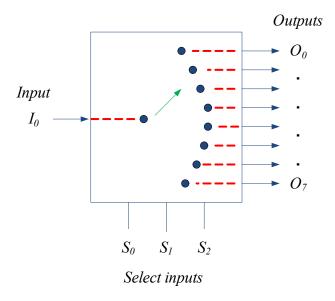

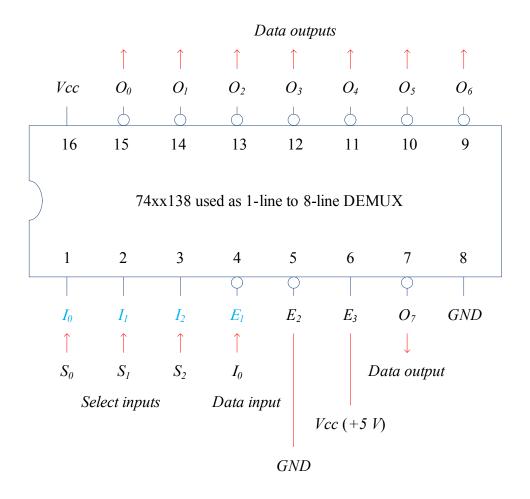

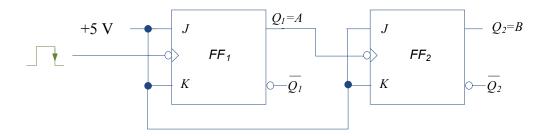

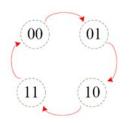

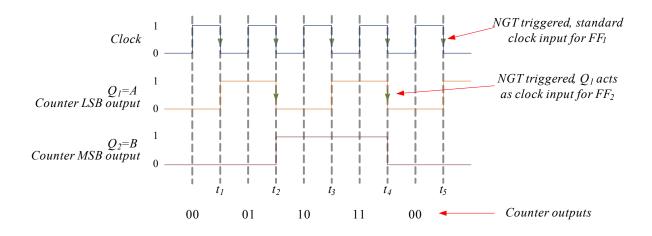

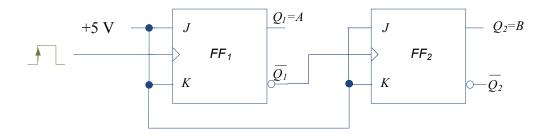

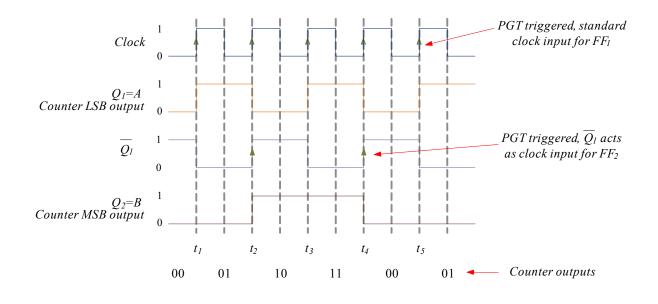

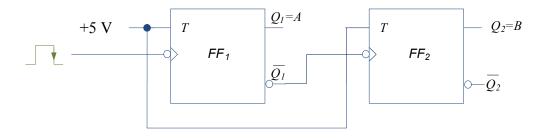

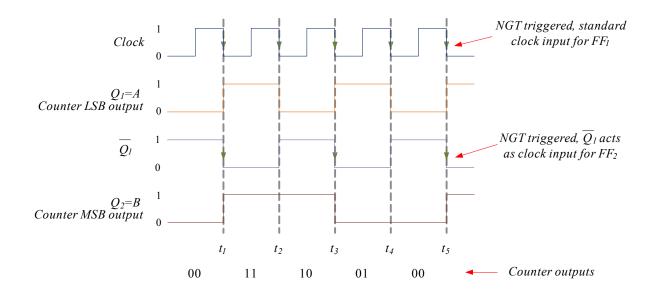

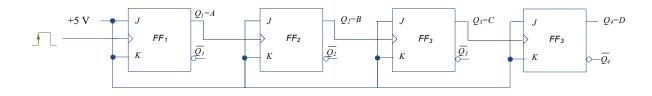

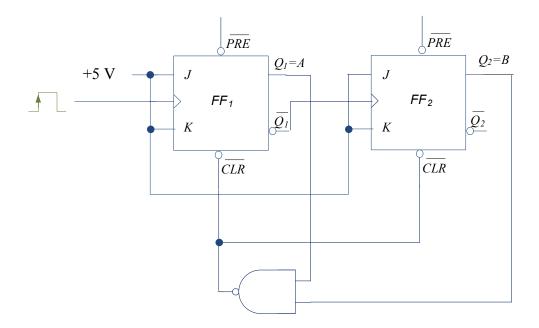

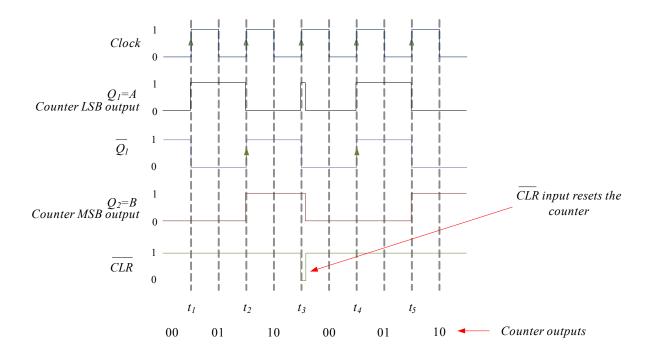

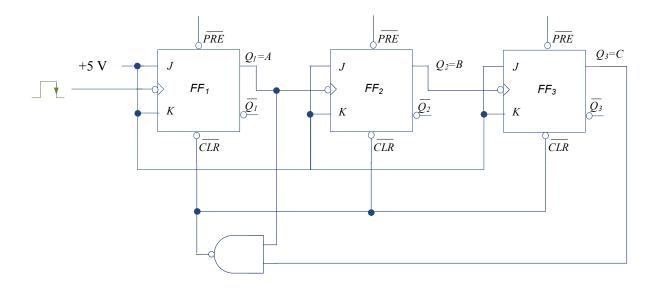

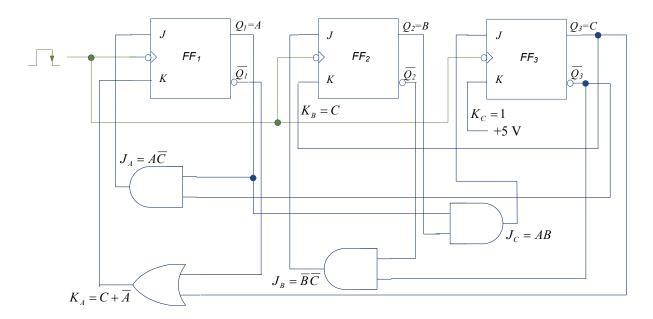

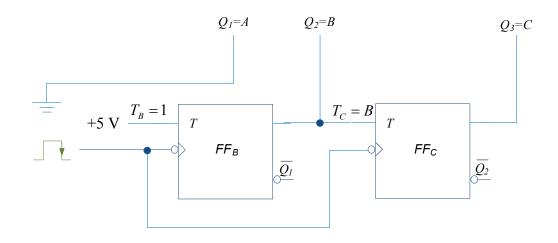

|-----------------------------|-----------------------------|-------------------------------------------------|