# Section 15. Input Capture

# HIGHLIGHTS

This section of the manual contains the following topics:

| 15.1  | Introduction                          | 15-2  |

|-------|---------------------------------------|-------|

| 15.2  | Input Capture Registers               |       |

| 15.3  | Timer Selection                       |       |

| 15.4  | Input Capture Enable                  |       |

| 15.5  | Input Capture Event Modes             |       |

| 15.6  | Capture Buffer Operation              | 15-14 |

| 15.7  | Input Capture Interrupts              | 15-15 |

| 15.8  | Operation in Power-Saving Modes       | 15-17 |

| 15.9  | Input Capture Operation in Debug Mode | 15-18 |

| 15.10 | I/O Pin Control                       | 15-18 |

| 15.11 | Design Tips                           | 15-18 |

| 15.12 | Related Application Notes             | 15-19 |

| 15.13 | Revision History                      |       |

15

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all PIC32 devices.

Please consult the note at the beginning of the **"Input Capture"** chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

# 15.1 INTRODUCTION

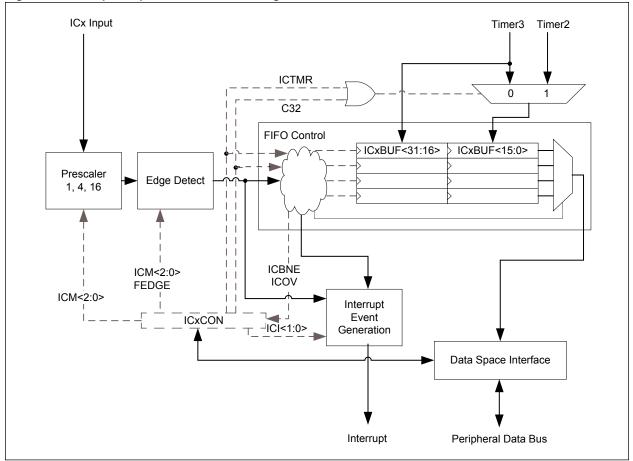

This section describes the Input Capture module and its associated operational modes. The Input Capture module is used to capture a timer value from one of two selectable time bases on the occurrence of an event on an input pin. The Input Capture features are useful in applications requiring frequency (Time Period) and pulse measurement. Figure 15-1 depicts a simplified block diagram of the Input Capture module.

| Note: | Each PIC32 device variant may have one or more Input Capture modules. Refer to         |

|-------|----------------------------------------------------------------------------------------|

|       | the specific device data sheet for information on the number of Input Capture          |

|       | modules available in a particular device.                                              |

|       | All Input Capture modules are functionally identical. In this document, an 'x' used in |

|       | the names of pins, Control/Status bits, and registers denotes the specific Input       |

|       | Capture module.                                                                        |

The Input Capture module has multiple operating modes, which are selected via the ICxCON register. The operating modes include the following:

- Capture timer value on every falling edge of input applied at the ICx pin

- · Capture timer value on every rising edge of input applied at the ICx pin

- · Capture timer value on every fourth rising edge of input applied at the ICx pin

- · Capture timer value on every sixteenth rising edge of input applied at the ICx pin

- Capture timer value on every rising and falling edge of input applied at the ICx pin

- · Capture timer value on the specified edge and every edge thereafter

The Input Capture module has a four-level First In First Out (FIFO) buffer. The number of capture events required to generate a CPU interrupt can be selected by the user application. An Input Capture module can also be configured to generate a CPU interrupt on a rising edge of the capture input when the device is in Sleep or Idle mode.

Figure 15-1: Input Capture Module Block Diagram

# 15.2 INPUT CAPTURE REGISTERS

Each Input Capture module available on PIC32 devices has the following Special Function Registers (SFRs):

- ICxCON: Input Capture x Control Register<sup>(1,2,3)</sup>

- ICxBUF: Input Capture x Buffer Register

Each Input Capture module also has the following associated bits for interrupt control:

- Interrupt Enable Control bit (ICxIE)

- Interrupt Flag Status bit (ICxIF)

- Interrupt Priority Control bits (ICxIP)

- Interrupt Subpriority Control bits (ICxIS)

Table 15-1 provides a brief summary of the Input Capture related registers, and is followed by a detailed description of each register.

| Address<br>Offset | Name                      |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------|---------------------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 0x00              | ICxCON <sup>(1,2,3)</sup> | 31:24 | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |

|                   |                           | 23:16 | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |

|                   |                           | 15:8  | ON                | FRZ               | SIDL              | —                 | —                 | —                 | FEDGE            | C32              |

|                   |                           | 7:0   | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

| 0x10              | ICxBUF                    | 31:24 |                   |                   |                   | ICxBUF            | <31:24>           |                   |                  |                  |

|                   |                           | 23:16 |                   |                   |                   |                   | ICxBUF<23:16>     |                   |                  |                  |

|                   |                           | 15:8  |                   |                   |                   | ICxBUF<15:8>      |                   |                   |                  |                  |

|                   |                           | 7:0   |                   |                   |                   |                   | ICxBUF<7:0>       |                   |                  |                  |

Table 15-1: Input Capture SFR Summary

Legend: — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

**Note** 1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., ICxCONCLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g., ICxCONSET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., ICxCONINV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

| U-0                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                  | U-0                                                                                                                                                                           | U-0                                                                                                                                                  | U-0                                                                                                                             |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| —                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                | _                                                                                                                                                                                    | —                                                                                                                                                                             | _                                                                                                                                                    | —                                                                                                                               |

| oit 31                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                                                                      | bit 24                                                                                                                          |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                                                                      |                                                                                                                                 |

| U-0                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                  | U-0                                                                                                                                                                           | U-0                                                                                                                                                  | U-0                                                                                                                             |

| —                                                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                | _                                                                                                                                                                                    | —                                                                                                                                                                             | _                                                                                                                                                    | —                                                                                                                               |

| bit 23                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                                                                      | bit 16                                                                                                                          |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                                                                      |                                                                                                                                 |

| R/W-0                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                  | U-0                                                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                           |

| ON                                                                              | FRZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                                | _                                                                                                                                                                                    | —                                                                                                                                                                             | FEDGE                                                                                                                                                | C32                                                                                                                             |

| bit 15                                                                          | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                               | 1                                                                                                                                                    | bit 8                                                                                                                           |

|                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                                                                      |                                                                                                                                 |

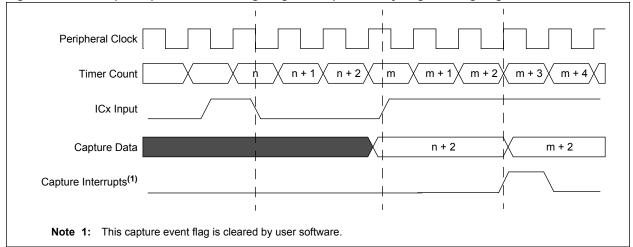

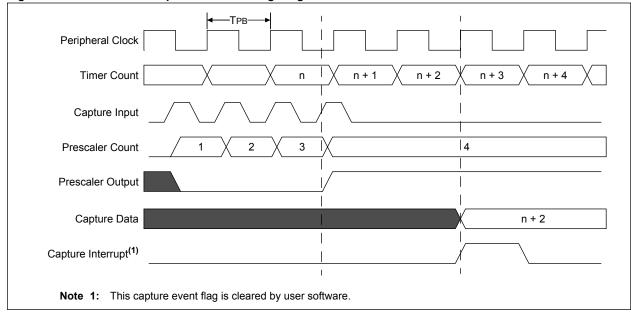

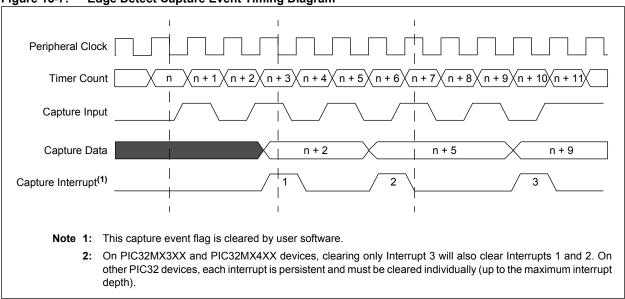

| R/W-0                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R-0                                                                                                                                                                                                                                                              | R-0                                                                                                                                                                                  | R/W-0                                                                                                                                                                         | R/W-0                                                                                                                                                | R/W-0                                                                                                                           |