## Section 31. DMA Controller

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 31.1 | Introduction                              |  |

|------|-------------------------------------------|--|

| 31.2 | Status and Control Registers              |  |

| 31.3 | Modes of Operation                        |  |

| 31.4 | Interrupts                                |  |

| 31.5 | Operation in Power-Saving and Debug Modes |  |

| 31.6 | Effects of Various Resets                 |  |

| 31.7 | Related Application Notes                 |  |

| 31.8 | Revision History                          |  |

Note: This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all PIC32MX devices.

Please consult the note at the beginning of the "Direct Memory Access (DMA) Controller" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

### 31.1 INTRODUCTION

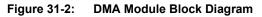

The Direct Memory Access (DMA) controller is a bus master module that is useful for data transfers between different peripherals without intervention from the CPU. The source and destination of a DMA transfer can be any of the memory-mapped modules included in the PIC32MX. For example, memory, or one of the Peripheral Bus (PBUS) devices such as SPI, UART and so on.

Following are some of the key features of the DMA module:

- Depending on the device variant, up to eight identical channels are available, including the following:

- Auto-Increment Source and Destination Address registers

- Source and Destination Pointers

- · Depending on the device variant, data transfers of up to 64 Kbytes are supported

- Automatic Word-Size Detection, featuring the following:

- Transfer granularity down to byte level

- Bytes need not be word-aligned at source and destination

- · Fixed Priority Channel Arbitration

- · Flexible DMA Channel Operating modes, including the following:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA Requests, featuring the following:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Automatic transfer termination upon a data pattern match

- Multiple DMA Channel Status Interrupts, supplying the following:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA Debug Support Features, including the following:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

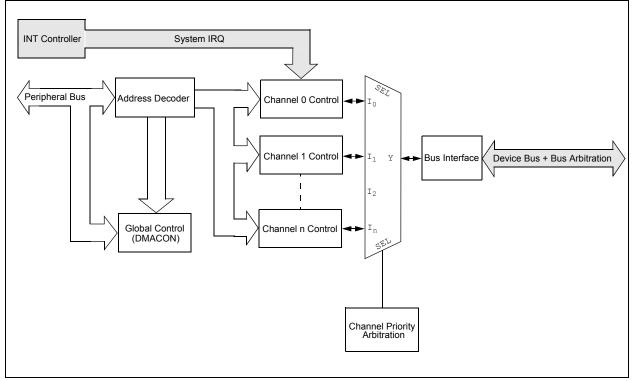

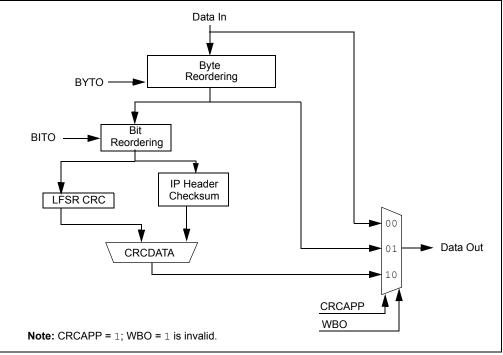

- · CRC Generation Module, featuring the following:

- CRC module can be assigned to any of the available channels

- Data read from the source can be reordered on some device variants

- CRC module is highly configurable

The following features are also available in the DMA controller:

- Unaligned Transfers

- · Different Source and Destination Sizes

- Memory-to-Memory Transfers

- · Memory-to-Peripheral Transfers

- Channel Auto-Enable

- Events Start/Stop

- Pattern Match Detection

- Channel Chaining

- CRC Calculation

#### 31.1.1 DMA Operation

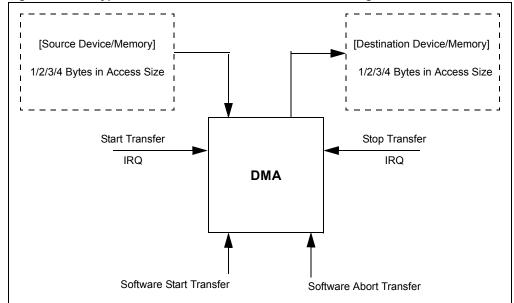

A DMA channel transfers data from a source to a destination without CPU intervention. The source and destination start addresses define the start address of the source and destination, respectively.

Both the source and destination have independently configurable sizes and the number of the transferred bytes is independent of the source and destination sizes.

A transfer is initiated either by software or by an interrupt request. The user can select any interrupt on the device to start a DMA transfer.

Upon transfer initiation, the DMA controller will perform a cell transfer and the channel remains enabled until a block transfer is complete. When a channel is disabled, further transfers will be prohibited until the channel is re-enabled.

The DMA channel uses separate pointers to keep track of the current word locations at the source and destination.

Interrupts can be generated when the source/destination pointer is half of the source/destination size, or when the source/destination counter reaches the end of the source/destination.

A DMA transfer can be aborted by the software, by a pattern match or by an interrupt event. The transfer will also stop when an address error is detected.

Figure 31-1: Typical DMA Source to Destination Transfer Diagram

## 31.2 STATUS AND CONTROL REGISTERS

**Note:** Each PIC32MX device variant may have one or more DMA channels. An 'x' used in the names of Control/Status bits and registers denotes the particular channel. Refer to the specific device data sheets for more details.

The DMA module consists of the following Special Function Registers (SFRs):

- DMACON: DMA Controller Control Register(1,2,3)

- DMASTAT: DMA Status Register(1)

- DMAADDR: DMA Address Register(1)

- DCRCCON: DMA CRC Control Register(1,2,3)

- DCRCDATA: DMA CRC Data Register(1,2,3) The initial value of the CRC generator

- DCRCXOR: DMA CRCXOR Enable Register(1,2,3) Provides a description of the generator polynomial for CRC calculation

- DCHxCON: DMA Channel x Control Register(1,2,3)

- DCHxECON: DMA Channel x Event Control Register(1,2,3)

- DCHxINT: DMA Channel x Interrupt Control Register(1,2,3)

- DCHxSSA: DMA Channel x Source Start Address Register(1,2,3)

- DCHxDSA: DMA Channel x Destination Start Address Register

- DCHxSSIZ: DMA Channel x Source Size Register(1,2,3)

- DCHxDSIZ: DMA Channel x Destination Size Register(1,2,3)

- DCHxSPTR: DMA Channel x Source Pointer Register(1)

- DCHxDPTR: DMA Channel x Destination Pointer Register

- DCHxCSIZ: DMA Channel x Cell-Size Register(1,2,3)

- DCHxCPTR: DMA Channel x Cell Pointer Register(1)

- DCHxDAT: DMA Channel x Pattern Data Register(1,2,3)

Table 31-1 provides a brief summary of DMA-module-related registers. Corresponding registers appear after the summary, followed by a detailed description of each register.

| Address | -1: DMA Re                  | Bit   | Bit                            | Bit                            | Bit                   | Bit                  | Bit                    | Bit                      | Bit                     | Bit                 |  |  |  |

|---------|-----------------------------|-------|--------------------------------|--------------------------------|-----------------------|----------------------|------------------------|--------------------------|-------------------------|---------------------|--|--|--|

| Offset  | Name                        | Range | 31/23/15/7                     | 30/22/14/6                     | 29/21/13/5            | 28/20/12/4           | 27/19/11/3             | 26/18/10/2               | 25/17/9/1               | 24/16/8/0           |  |  |  |

| 0x00    | DMACON <sup>(1,2,3)</sup>   | 31:24 | —                              | _                              | -                     | -                    | —                      | _                        | —                       | -                   |  |  |  |

|         |                             | 23:16 | —                              | —                              | —                     | _                    | —                      | _                        | _                       | —                   |  |  |  |

|         |                             | 15:8  | ON                             | FRZ                            | SIDL <sup>(4)</sup>   | SUSPEND              | DMABUSY <sup>(4)</sup> | _                        | _                       | _                   |  |  |  |

|         |                             | 7:0   | _                              | _                              | _                     | _                    | —                      | _                        | _                       | _                   |  |  |  |

| 0x10    | DMASTAT                     | 31:24 | _                              | _                              | _                     | _                    | _                      | _                        | _                       | _                   |  |  |  |

|         |                             | 23:16 | _                              | _                              | _                     | _                    | —                      | _                        | _                       | _                   |  |  |  |

|         |                             | 15:8  |                                | _                              | _                     | _                    | _                      | _                        | —                       | _                   |  |  |  |

|         |                             | 7:0   | _                              | _                              | _                     | _                    | RDWR                   | D                        | MACH<2:0>(              | 5)                  |  |  |  |

| 0x20    | DMAADDR                     | 31:24 |                                |                                |                       | DMAAD                | DR<31:24>              |                          |                         |                     |  |  |  |

|         |                             | 23:16 |                                |                                |                       | DMAAD                | DR<23:16>              |                          |                         |                     |  |  |  |

|         |                             | 15:8  |                                |                                |                       | DMAAD                | DR<15:8>               |                          |                         |                     |  |  |  |

|         |                             | 7:0   |                                |                                |                       | DMAAD                | )DR<7:0>               |                          |                         |                     |  |  |  |

| 0x30    | DCRCCON <sup>(1,2,3)</sup>  | 31:24 | _                              | _                              | BYTO1 <sup>(4)</sup>  | BYTO0 <sup>(4)</sup> | WBO <sup>(4)</sup>     | _                        | _                       | BITO <sup>(4)</sup> |  |  |  |

|         |                             | 23:16 | _                              | _                              | _                     | _                    | _                      | _                        | _                       | _                   |  |  |  |

|         |                             | 15:8  | _                              | _                              | _                     |                      | F                      | PLEN<4:0> <sup>(5)</sup> |                         |                     |  |  |  |

|         |                             | 7:0   | CRCEN                          | CRCAPP                         | CRCTYP <sup>(4)</sup> | _                    | _                      | C                        | RCCH<2:0> <sup>(!</sup> | 5)                  |  |  |  |

| 0x40    | DCRCDATA <sup>(1,2,3)</sup> | 31:24 |                                | DCRCDATA<31:24> <sup>(5)</sup> |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 23:16 | DCRCDATA<23:16> <sup>(5)</sup> |                                |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 15:8  | DCRCDATA<15:8> <sup>(5)</sup>  |                                |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 7:0   |                                | DCRCDATA<7:0> <sup>(5)</sup>   |                       |                      |                        |                          |                         |                     |  |  |  |

| 0x50    | DCRCXOR <sup>(1,2,3)</sup>  | 31:24 | DCRCXOR<31:24> <sup>(5)</sup>  |                                |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 23:16 | DCRCXOR<23:16> <sup>(5)</sup>  |                                |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 15:8  |                                | DCRCXOR<15:8> <sup>(5)</sup>   |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 7:0   |                                |                                |                       | DCRCX                | OR<7:0> <sup>(5)</sup> |                          |                         |                     |  |  |  |

| 0x60    | DCHxCON <sup>(1,2,3)</sup>  | 31:24 | _                              | —                              | —                     | _                    | —                      | _                        | —                       | —                   |  |  |  |

|         |                             | 23:16 | _                              | _                              | _                     | _                    | _                      | _                        | _                       | _                   |  |  |  |

|         |                             | 15:8  | CHBUSY <sup>(4)</sup>          | _                              | _                     | _                    | _                      | _                        | _                       | CHCHNS              |  |  |  |

|         |                             | 7:0   | CHEN                           | CHAED                          | CHCHN                 | CHAEN                | _                      | CHEDET                   | CHPR                    | l<1:0>              |  |  |  |

| 0x70    | DCHxECON <sup>(1,2,3)</sup> | 31:24 | —                              | —                              | —                     | —                    | _                      | -                        | —                       | —                   |  |  |  |

|         |                             | 23:16 |                                |                                |                       | CHAIF                | RQ<7:0>                |                          |                         |                     |  |  |  |

|         |                             | 15:8  |                                |                                |                       | CHSIF                | RQ<7:0>                |                          |                         |                     |  |  |  |

|         |                             | 7:0   | CFORCE                         | CABORT                         | PATEN                 | SIRQEN               | AIRQEN                 | —                        | _                       | —                   |  |  |  |

| 0x80    | DCHxINT <sup>(1,2,3)</sup>  | 31:24 | _                              | _                              | _                     | _                    | _                      | _                        | _                       | _                   |  |  |  |

|         |                             | 23:16 | CHSDIE                         | CHSHIE                         | CHDDIE                | CHDHIE               | CHBCIE                 | CHCCIE                   | CHTAIE                  | CHERIE              |  |  |  |

|         |                             | 15:8  | _                              | _                              | _                     | _                    | _                      | _                        | _                       | _                   |  |  |  |

| ļ       |                             | 7:0   | CHSDIF                         | CHSHIF                         | CHDDIF                | CHDHIF               | CHBCIF                 | CHCCIF                   | CHTAIF                  | CHERIF              |  |  |  |

| 0x90    | DCHxSSA <sup>(1,2,3)</sup>  | 31:24 |                                |                                | I                     | CHSSA                | \<31:24>               |                          |                         | I                   |  |  |  |

|         |                             | 23:16 |                                |                                |                       | CHSSA                | <23 <sup>.</sup> 16>   |                          |                         |                     |  |  |  |

| ·       |                             | 23.10 |                                |                                |                       |                      |                        |                          |                         |                     |  |  |  |

|         |                             | 15:8  |                                | CHSSA<15:8>                    |                       |                      |                        |                          |                         |                     |  |  |  |

#### Table 31-1: DMA Register Summary

Legend:

**d:** — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

Note 1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., DMACONCLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g., DMACONSET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., DMACONINV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

4: This bit is not available on all devices. Refer to the specific device data sheet for more details.

5: Depending on the device variant, not all bits are available. Refer to the specific device data sheet for more details.

| -1: DMAR                    |                                                                                                                                                             | l I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · ·                                                                                 |                                                                                                               | Dit                                                                                                                                     | Dit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Dit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name                        | Bit<br>Range                                                                                                                                                | Bit<br>31/23/15/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bit<br>30/22/14/6                                                                   | Bit<br>29/21/13/5                                                                                             | Bit<br>28/20/12/4                                                                                                                       | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>26/18/10/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| DCHxDSA                     | 31:24                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |                                                                                                               | CHDSA                                                                                                                                   | <31:24>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                             | 23:16                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |                                                                                                               | CHDSA                                                                                                                                   | <23:16>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                             | 15:8                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |                                                                                                               | CHDS                                                                                                                                    | 4<15:8>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                             | 7:0                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                     |                                                                                                               | CHDS                                                                                                                                    | A<7:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| DCHxSSIZ <sup>(1,2,3)</sup> | 31:24                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                   |                                                                                                               | _                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                             | 23:16                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                   |                                                                                                               | _                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |