# Section 26. Op amp/Comparator

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 26.1 | Introduction                           |  |

|------|----------------------------------------|--|

| 26.2 | Comparator Registers                   |  |

| 26.3 | Comparator Operation                   |  |

| 26.4 | Comparator Configuration               |  |

| 26.5 | Comparator Interrupts                  |  |

| 26.6 | Op amp Configuration                   |  |

| 26.7 | Comparator Voltage Reference Generator |  |

| 26.8 | Related Application Notes              |  |

| 26.9 | Revision History                       |  |

|      |                                        |  |

Note: This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33E/PIC24E devices.

Please consult the note at the beginning of the "**Comparator**" or "**Op amp/Comparator**" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

## 26.1 INTRODUCTION

The dsPIC33E/PIC24E devices have multiple built-in comparators, some of which can be also configured as op amps, with their output being brought to an external pin for gain/filtering connections.

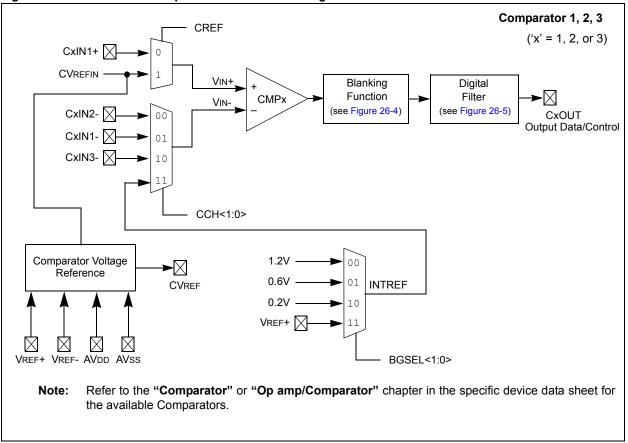

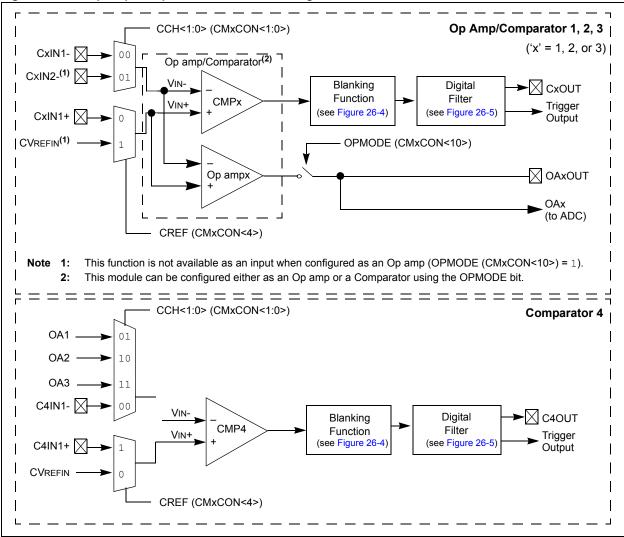

As illustrated in Figure 26-1 and Figure 26-2, individual comparator and op amp options are specified by the module's Special Function Register (SFR) control bits. These options allow users to:

- Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- Configure the band gap

- · Configure output blanking and masking

- Configure as a comparator or op amp

| This document references both the Op amp/Comparator and the dedicated         |

|-------------------------------------------------------------------------------|

| Comparator modules for the dsPIC33E/PIC24E family of devices. Refer the "Com- |

| parator" or "Op amp/Comparator" chapter in the specific device data sheet for |

| the availability of these features.                                           |

2: Throughout this document when the comparator is referenced it applies to both the dedicated Comparator module as well as the Op amp/Comparator module when configured as a Comparator.

The Op amp/Comparator and Comparator operating modes are configured through the CMxCON registers. Some of the options include Op amp or Comparator mode, polarity selection of the comparator and inverting/non-inverting comparator polarity, as well as input selection options.

An option is also available to use the internal reference voltage that is generated by a resistor ladder network, which is configured by the Comparator Voltage Reference Control (CVRCON) register (see Register 26-6).

Figure 26-1: Dedicated Comparator Module Block Diagram

Figure 26-2: Op amp/Comparator Module Block Diagram

## 26.2 COMPARATOR REGISTERS

The Comparator module uses the following six registers:

CMSTAT: Comparator Status Register

This register enables control over the operation of all comparators when the device enters ldle mode. In addition, it provides the status of all comparator results, as well as all of the comparator outputs and event bits, which are replicated as read-only bits in the CMSTAT register.

CMxCON: Op amp/Comparator Control Register

This register allows the application program to enable, configure, and interact with the individual comparators/op amps (on some devices).

CMxMSKSRC: Comparator Mask Source Select Control Register

This register allows the application program to select sources for the inputs to the blanking function.

- CMxMSKCON: Comparator Mask Gating Control Register

- This register allows the application program to specify the blank function logic.

- CMxFLTR: Comparator Filter Control Register

This register enables comparator filter configuration.

CVRCON: Comparator Voltage Reference Control Register

This register allows the application program to enable, configure and interact with the comparator internal voltage reference generator (for more information, see **26.7** "Comparator Voltage Reference Generator").

| Register 26-1 | : CMSTAT: Comparator Status Register                 |                                      |                |                      |                  |                 |       |  |  |  |

|---------------|------------------------------------------------------|--------------------------------------|----------------|----------------------|------------------|-----------------|-------|--|--|--|

| R/W-0         | U-0                                                  | U-0                                  | U-0            | R-0                  | R-0              | R-0             | R-0   |  |  |  |

| CMSIDL        |                                                      |                                      |                | C4EVT <sup>(1)</sup> | C3EVT            | C2EVT           | C1EVT |  |  |  |

| bit 15        |                                                      |                                      |                |                      |                  |                 | bit   |  |  |  |

| U-0           | U-0                                                  | U-0                                  | U-0            | R-0                  | R-0              | R-0             | R-0   |  |  |  |

|               |                                                      |                                      |                | C4OUT <sup>(1)</sup> | C3OUT            | C2OUT           | C1OUT |  |  |  |

| bit 7         |                                                      |                                      |                | 04001                | 00001            | 02001           | bit   |  |  |  |

| Legend:       |                                                      |                                      |                |                      |                  |                 |       |  |  |  |

| R = Readable  | e hit                                                | W = Writable                         | hit            | II = I Inimplem      | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value at |                                                      | '1' = Bit is se                      |                | '0' = Bit is clea    |                  | x = Bit is unkr | nown  |  |  |  |

|               |                                                      |                                      | •              |                      |                  |                 |       |  |  |  |

| bit 15        | CMSIDL: Sto                                          | op in Idle Mode                      | bit            |                      |                  |                 |       |  |  |  |

|               |                                                      |                                      |                | tors when device     | e enters Idle mo | ode             |       |  |  |  |

|               |                                                      | operation of a                       | -              | s in Idle mode       |                  |                 |       |  |  |  |

| bit 14-12     | •                                                    | nted: Read as                        |                |                      |                  |                 |       |  |  |  |

| bit 11        |                                                      | parator 4 Ever                       |                |                      |                  |                 |       |  |  |  |

|               |                                                      | Comparator ev                        |                |                      |                  |                 |       |  |  |  |

|               | 0 = Op amp/                                          | Comparator ev                        | ent did not or | ccur                 |                  |                 |       |  |  |  |

| bit 10        | C3EVT: Comparator 3 Event Status bit                 |                                      |                |                      |                  |                 |       |  |  |  |

|               | 1 = Compara                                          | 1 = Comparator event occurred        |                |                      |                  |                 |       |  |  |  |

|               | 0 = Comparator event did not occur                   |                                      |                |                      |                  |                 |       |  |  |  |

| bit 9         | C2EVT: Comparator 2 Event Status bit                 |                                      |                |                      |                  |                 |       |  |  |  |

|               | 1 = Compara                                          | 1 = Comparator event occurred        |                |                      |                  |                 |       |  |  |  |

|               | 0 = Comparator event did not occur                   |                                      |                |                      |                  |                 |       |  |  |  |

| bit 8         | C1EVT: Com                                           | C1EVT: Comparator 1 Event Status bit |                |                      |                  |                 |       |  |  |  |

|               | 1 = Compara                                          | 1 = Comparator event occurred        |                |                      |                  |                 |       |  |  |  |

|               | 0 = Compara                                          | ator event did n                     | ot occur       |                      |                  |                 |       |  |  |  |

| bit 7-4       | Unimplemer                                           | nted: Read as                        | 'O'            |                      |                  |                 |       |  |  |  |

| bit 3         | C4OUT: Comparator 4 Output Status bit <sup>(1)</sup> |                                      |                |                      |                  |                 |       |  |  |  |

|               | When CPOL = 0:                                       |                                      |                |                      |                  |                 |       |  |  |  |

|               | 1 = VIN + > VIN-                                     |                                      |                |                      |                  |                 |       |  |  |  |

|               | 0 = VIN+ < VIN-                                      |                                      |                |                      |                  |                 |       |  |  |  |

|               | When CPOL = 1:                                       |                                      |                |                      |                  |                 |       |  |  |  |

|               | 1 = VIN + < VIN                                      |                                      |                |                      |                  |                 |       |  |  |  |

|               | 0 = VIN + > VIN -                                    |                                      |                |                      |                  |                 |       |  |  |  |

| bit 2         | C3OUT: Comparator 3 Output Status bit                |                                      |                |                      |                  |                 |       |  |  |  |

|               | When CPOL = $0$ :                                    |                                      |                |                      |                  |                 |       |  |  |  |

|               | 1 = VIN+ > VIN-                                      |                                      |                |                      |                  |                 |       |  |  |  |

|               | 0 = VIN+ < V                                         | IN-                                  |                |                      |                  |                 |       |  |  |  |

|               |                                                      |                                      |                |                      |                  |                 |       |  |  |  |

|               | When CPOL                                            | = 1:                                 |                |                      |                  |                 |       |  |  |  |

|               | <u>When CPOL</u><br>1 = VIN+ < V                     |                                      |                |                      |                  |                 |       |  |  |  |

Register 26-1: CMSTAT: Comparator Status Register

Note 1: This bit is not available on all devices. Refer to the "Comparator" or "Op amp/Comparator" chapter in the specific device data sheet for availability.

#### Register 26-1: CMSTAT: Comparator Status Register (Continued)

- bit 1 C2OUT: Comparator 2 Output Status bit When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN -When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN bit 0 C1OUT: Comparator 1 Output Status bit When CPOL = 0: 1 = VIN + > VIN -0 = VIN + < VIN -When CPOL = 1: 1 = VIN + < VIN-0 = VIN + > VIN -

- Note 1: This bit is not available on all devices. Refer to the "Comparator" or "Op amp/Comparator" chapter in the specific device data sheet for availability.

26

# dsPIC33E/PIC24E Family Reference Manual

| R/W-0        | R/W-0                                                                                                                               | R/W-0           | U-0                 | U-0              | R/W-0                 | R/W-0           | R/W-0 |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|------------------|-----------------------|-----------------|-------|--|--|--|

| CON          | COE                                                                                                                                 | CPOL            | _                   | —                | OPMODE <sup>(1)</sup> | CEVT            | COUT  |  |  |  |

| bit 15       |                                                                                                                                     | •               |                     |                  |                       |                 | bit 8 |  |  |  |

|              |                                                                                                                                     |                 |                     |                  |                       |                 |       |  |  |  |

| R/W-0        | R/W-0                                                                                                                               | U-0             | R/W-0               | U-0              | U-0                   | R/W-0           | R/W-0 |  |  |  |

|              | POL<1:0>                                                                                                                            | _               | CREF <sup>(2)</sup> | _                | —                     | CCH             |       |  |  |  |

| bit 7        |                                                                                                                                     |                 |                     |                  |                       |                 | bit ( |  |  |  |

| Legend:      |                                                                                                                                     |                 |                     |                  |                       |                 |       |  |  |  |

| R = Readab   | le bit                                                                                                                              | W = Writable    | bit                 | U = Unimple      | mented bit, read a    | as '0'          |       |  |  |  |

| -n = Value a | It POR                                                                                                                              | '1' = Bit is se | t                   | '0' = Bit is cle | ared                  | x = Bit is unkr | nown  |  |  |  |

|              |                                                                                                                                     |                 |                     |                  |                       |                 |       |  |  |  |

| bit 15       | CON: Compa                                                                                                                          | rator Enable b  | it                  |                  |                       |                 |       |  |  |  |

|              | 1 = Comparator is enabled                                                                                                           |                 |                     |                  |                       |                 |       |  |  |  |

|              | 0 = Comparator is disabled                                                                                                          |                 |                     |                  |                       |                 |       |  |  |  |

| bit 14       | COE: Comparator Output Enable bit                                                                                                   |                 |                     |                  |                       |                 |       |  |  |  |

|              | <ul> <li>1 = Comparator output is present on the CxOUT pin</li> <li>0 = Comparator output is internal only</li> </ul>               |                 |                     |                  |                       |                 |       |  |  |  |

| bit 13       |                                                                                                                                     |                 |                     |                  |                       |                 |       |  |  |  |

|              | <b>CPOL:</b> Comparator Output Polarity Select bit<br>1 = Comparator output is inverted                                             |                 |                     |                  |                       |                 |       |  |  |  |

|              |                                                                                                                                     | or output is no |                     |                  |                       |                 |       |  |  |  |

| bit 12-11    | Unimplemen                                                                                                                          | ted: Read as    | 0'                  |                  |                       |                 |       |  |  |  |

| bit 10       | <b>OPMODE:</b> Op Amp/Comparator Operation Mode Select bit <sup>(1)</sup>                                                           |                 |                     |                  |                       |                 |       |  |  |  |

|              | 1 = Circuit operates as an Op amp                                                                                                   |                 |                     |                  |                       |                 |       |  |  |  |

|              | •                                                                                                                                   | erates as a Co  | •                   |                  |                       |                 |       |  |  |  |

| bit 9        | <b>CEVT</b> : Comparator Event bit                                                                                                  |                 |                     |                  |                       |                 |       |  |  |  |

|              | 1 = Comparator event according to EVPOL<1:0> settings occurred; disables future triggers and<br>interrupts until the bit is cleared |                 |                     |                  |                       |                 |       |  |  |  |

|              | 0 = Comparator event did not occur                                                                                                  |                 |                     |                  |                       |                 |       |  |  |  |

| bit 8        | <b>COUT:</b> Comparator Output bit                                                                                                  |                 |                     |                  |                       |                 |       |  |  |  |

|              | When CPOL = 0 (non-inverted polarity):                                                                                              |                 |                     |                  |                       |                 |       |  |  |  |

|              | 1 = VIN + > VIN-                                                                                                                    |                 |                     |                  |                       |                 |       |  |  |  |

|              | 0 = VIN+ < VIN-<br>When CPOL = 1 (inverted polarity):                                                                               |                 |                     |                  |                       |                 |       |  |  |  |

|              | $\frac{\text{VNen CPOL}}{1 = \text{VIN} + < \text{VIN}}$                                                                            |                 | olarity):           |                  |                       |                 |       |  |  |  |

|              |                                                                                                                                     | N               |                     |                  |                       |                 |       |  |  |  |

- Note 1: This bit not available on all devices. Refer to the "Comparator" or "Op amp/Comparator" chapter in the specific device data sheet for availability.

- 2: Inputs that are selected and not available will be tied to Vss.

- **3:** This input is not available when OPMODE (CMxCON<10>) = 1.

| Register 26-2: | CMxCON: Op amp/Comparator Control Register (Continued)                                                                                                                                                                                                        |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6        | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|                | <ul> <li>11 = Trigger/Event/Interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/Event/Interrupt generated only on high to low transition of the polarity-selected comparator output (while CEVT = 0)</li> </ul> |

|                | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                           |

|                | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output                                                                                                                                                                       |

|                | 01 = Trigger/Event/Interrupt generated only on low to high transition of the polarity-selected<br>comparator output (while CEVT = 0)                                                                                                                          |

|                | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output                                                                                                                                                                           |

|                | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output<br>00 = Trigger/Event/Interrupt generation is disabled                                                                                                                |

| bit 5          | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4          | CREF: Comparator Reference Select bit (VIN+ input) <sup>(2)</sup>                                                                                                                                                                                             |

|                | 1 = VIN+ input connects to internal CVREFIN voltage <sup>(3)</sup><br>0 = VIN+ input connects to CxIN1+ pin                                                                                                                                                   |

| bit 3-2        | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0        | CCH<1:0>: Op amp/Comparator Channel Select bits <sup>(2)</sup>                                                                                                                                                                                                |

|                | These bits select the CxIN1, CxIN2, and CxIN3 inputs. Refer to the <b>"Comparator"</b> or <b>"Op amp/Comparator"</b> chapter in the specific device data sheet for the available selections.                                                                  |

| Note 1: Thi    | s bit not available on all devices. Refer to the "Comparator" or "Op amp/Comparator" chapter in the                                                                                                                                                           |

- ne specific device data sheet for availability.

- 2: Inputs that are selected and not available will be tied to Vss.

- **3:** This input is not available when OPMODE (CMxCON<10>) = 1.

26

| U-0                                | U-0   | U-0     | U-0                                     | R/W-0        | R/W-0 | R/W-0   | RW-0  |

|------------------------------------|-------|---------|-----------------------------------------|--------------|-------|---------|-------|

| —                                  | —     | —       | _                                       |              | SELSR | CC<3:0> |       |

| bit 15                             |       |         |                                         |              |       |         | bit 8 |

|                                    |       |         |                                         |              |       |         |       |

| R/W-0                              | R/W-0 | R/W-0   | R/W-0                                   | R/W-0        | R/W-0 | R/W-0   | R/W-0 |

|                                    | SELSR | CB<3:0> |                                         | SELSRCA<3:0> |       |         |       |

| bit 7                              |       |         |                                         |              |       |         | bit 0 |

|                                    |       |         |                                         |              |       |         |       |

| Legend:                            |       |         |                                         |              |       |         |       |

| R = Readable bit W = Writable bit  |       |         | U = Unimplemented bit, read as '0'      |              |       |         |       |

| -n = Value at POR '1' = Bit is set |       |         | '0' = Bit is cleared x = Bit is unknown |              |       | nown    |       |

### Register 26-3: CMxMSKSRC: Comparator Mask Source Select Control Register

| bit 11-8 | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | These bits select the FLTx, PTGx, and PWMx inputs as mask sources. Refer to the " <b>Comparator</b> " or " <b>Op amp/Comparator</b> " chapter in the specific device data sheet for available selections. |

| bit 7-4  | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                    |

|          | These bits select the FLTx, PTGx, and PWMx inputs as mask sources. Refer to the " <b>Comparator</b> " or " <b>Op amp/Comparator</b> " chapter in the specific device data sheet for available selections. |

| bit 3-0  | SELSRCA<3:0>: Mask A Input Select bits                                                                                                                                                                    |

|          | These bits select the FLTx, PTGx, and PWMx inputs as mask sources. Refer to the " <b>Comparator</b> " or " <b>Op amp/Comparator</b> " chapter in the specific device data sheet for available selections. |

| Register 26-4:  | CMxMSKC                                    | ON: Comparat                                       | or Mask Gatir                                    | ng Control Re    | egister                              |                |       |  |  |

|-----------------|--------------------------------------------|----------------------------------------------------|--------------------------------------------------|------------------|--------------------------------------|----------------|-------|--|--|

| R/W-0           | U-0                                        | R/W-0                                              | R/W-0                                            | R/W-0            | R/W-0                                | R/W-0          | R/W-0 |  |  |

| HLMS            | _                                          | OCEN                                               | OCNEN                                            | OBEN             | OBNEN                                | OAEN           | OANEN |  |  |

| bit 15          |                                            |                                                    |                                                  |                  |                                      |                | bit 8 |  |  |

| R/W-0           | R/W-0                                      | R/W-0                                              | R/W-0                                            | R/W-0            | R/W-0                                | R/W-0          | R/W-0 |  |  |

| NAGS            | PAGS                                       | ACEN                                               | ACNEN                                            | ABEN             | ABNEN                                | AAEN           | AANEN |  |  |

| bit 7           |                                            | _                                                  |                                                  |                  |                                      |                | bit 0 |  |  |

| Legend:         |                                            |                                                    |                                                  |                  |                                      |                |       |  |  |

| R = Readable I  | nit                                        | W = Writable                                       | hit                                              | II – I Inimpler  | mented bit, read                     | as 'O'         |       |  |  |

| -n = Value at P |                                            | '1' = Bit is set                                   |                                                  | '0' = Bit is cle |                                      | x = Bit is unk | nown  |  |  |

|                 | UK                                         |                                                    |                                                  |                  | aleu                                 |                | nown  |  |  |

| bit 15          | 1 = The mask                               | king (blanking) t                                  |                                                  | vent any asse    | rted ('0') compa<br>rted ('1') compa |                |       |  |  |

| bit 14          | Unimplemer                                 | ted: Read as                                       | 0'                                               |                  |                                      |                |       |  |  |

| bit 13          | OCEN: OR G                                 | Gate C Input Er                                    | able bit                                         |                  |                                      |                |       |  |  |

|                 |                                            | onnected to OR<br>ot connected to                  |                                                  |                  |                                      |                |       |  |  |

| bit 12          | OCNEN: OR                                  | Gate C Input I                                     | nverted Enable                                   | e bit            |                                      |                |       |  |  |

|                 |                                            | MCI is connect<br>MCI is not conr                  | ed to OR gate<br>nected to OR g                  | ate              |                                      |                |       |  |  |

| bit 11          | OBEN: OR G                                 | Gate B Input Er                                    | able bit                                         |                  |                                      |                |       |  |  |

|                 | 1 = MBI is co                              | nnected to OR<br>t connected to                    | gate                                             |                  |                                      |                |       |  |  |

| bit 10          | OBNEN: OR Gate B Input Inverted Enable bit |                                                    |                                                  |                  |                                      |                |       |  |  |

|                 |                                            | MBI is connect<br>MBI is not conr                  | ed to OR gate<br>nected to OR g                  | ate              |                                      |                |       |  |  |

| bit 9           | OAEN: OR G                                 | Sate A Input Er                                    | able bit                                         |                  |                                      |                |       |  |  |

|                 |                                            | nnected to OR<br>of connected to                   | •                                                |                  |                                      |                |       |  |  |

| bit 8           | OANEN: OR                                  | Gate A Input I                                     | nverted Enable                                   | e bit            |                                      |                |       |  |  |

|                 |                                            | MAI is connect<br>MAI is not conr                  | ed to OR gate<br>nected to OR g                  | ate              |                                      |                |       |  |  |

| bit 7           | 1 = Inverted                               | ANDI is connec                                     | verted Enable<br>ted to OR gate<br>nnected to OR | 9                |                                      |                |       |  |  |

| bit 6           | 1 = ANDI is c                              | Gate Output E<br>connected to O<br>not connected t | R gate                                           |                  |                                      |                |       |  |  |

| bit 5           | ACEN: AND                                  | Gate C Input E                                     | nable bit                                        |                  |                                      |                |       |  |  |

|                 |                                            | onnected to AN of connected to                     |                                                  |                  |                                      |                |       |  |  |

| bit 4           |                                            |                                                    | Inverted Enab                                    | le bit           |                                      |                |       |  |  |

|                 | 1 = Inverted I                             | MCI is connect                                     | ed to AND gate<br>nected to AND                  | e                |                                      |                |       |  |  |

| bit 3           |                                            | Gate B Input E                                     |                                                  | ~                |                                      |                |       |  |  |

|                 |                                            | nnected to AN                                      |                                                  |                  |                                      |                |       |  |  |

| Register 26-4: | CMxMSKCON: Comparator Mask Gating Co | ntrol Registe |

|----------------|--------------------------------------|---------------|

|----------------|--------------------------------------|---------------|

### Register 26-4: CMxMSKCON: Comparator Mask Gating Control Register (Continued)

| bit 2 | <b>ABNEN:</b> AND Gate B Input Inverted Enable bit<br>1 = Inverted MBI is connected to AND gate                   |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | 0 = Inverted MBI is not connected to AND gate                                                                     |

| bit 1 | AAEN: AND Gate A Input Enable bit                                                                                 |

|       | <ul><li>1 = MAI is connected to AND gate</li><li>0 = MAI is not connected to AND gate</li></ul>                   |

| bit 0 | AANEN: AND Gate A Input Inverted Enable bit                                                                       |

|       | <ul><li>1 = Inverted MAI is connected to AND gate</li><li>0 = Inverted MAI is not connected to AND gate</li></ul> |

| U-0          | U-0                                                                                                                                                             | U-0                                                                                                 | U-0             | U-0               | U-0            | U-0             | I-0   |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|-------------------|----------------|-----------------|-------|--|--|

|              | _                                                                                                                                                               | _                                                                                                   | _               | _                 |                | _               | _     |  |  |

| oit 15       |                                                                                                                                                                 |                                                                                                     |                 |                   |                |                 | bit 8 |  |  |

|              | DAMA                                                                                                                                                            | DAMA                                                                                                | DAALO           | DAM 0             | <b>D</b> 444 0 | DAVA            | DAMA  |  |  |

| U-0          | R/W-0                                                                                                                                                           | R/W-0                                                                                               | R/W-0           | R/W-0             | R/W-0          | R/W-0           | R/W-0 |  |  |

|              |                                                                                                                                                                 | CFSEL<2:0>                                                                                          |                 | CFLTREN           |                | CFDIV<2:0>      |       |  |  |

| bit 7        |                                                                                                                                                                 |                                                                                                     |                 |                   |                |                 | bit C |  |  |

| Legend:      |                                                                                                                                                                 |                                                                                                     |                 |                   |                |                 |       |  |  |

| R = Readab   | le bit                                                                                                                                                          | W = Writable                                                                                        | bit             | U = Unimplem      | ented bit, rea | ad as '0'       |       |  |  |

| -n = Value a | t POR                                                                                                                                                           | '1' = Bit is set                                                                                    | :               | '0' = Bit is clea | red            | x = Bit is unkr | nown  |  |  |

|              | $111 = T5CLK^{(1)}$ $110 = T4CLK^{(1)}$ $101 = T3CLK^{(1)}$ $100 = T2CLK^{(1)}$ $011 = SYNCO2^{(2,4)}$ $010 = SYNCO1^{(2)}$ $001 = Fosc^{(3)}$ $000 = Fp^{(3)}$ |                                                                                                     |                 |                   |                |                 |       |  |  |

| bit 3        | <b>CFLTREN:</b> Comparator Filter Enable bit<br>1 = Digital filter enabled<br>0 = Digital filter disabled                                                       |                                                                                                     |                 |                   |                |                 |       |  |  |

| bit 2-0      |                                                                                                                                                                 | Divide 1:128<br>Divide 1:64<br>Divide 1:32<br>Divide 1:16<br>Divide 1:8<br>Divide 1:4<br>Divide 1:2 | ilter Clock Div | vide Select bits  |                |                 |       |  |  |

- Note 1: For more information, refer to the "Timer" chapter in the specific device data sheet or Section 11. "Timers" (DS70362) in the "dsPIC33E/PIC24E Family Reference Manual".

- For more information, refer to the "High-Speed PWM" chapter in the specific device data sheet or Section 14. "High-Speed PWM" (DS70645) in the "dsPIC33E/PIC24E Family Reference Manual".

- **3:** For more information, refer to the **"Oscillator"** chapter in the specific device data sheet or **Section 7. "Oscillator"** (DS70580) in the *"dsPIC33E/PIC24E Family Reference Manual"*.

- 4: This bit setting is not available on all devices. Refer to the "Comparator" or "Op amp/Comparator" chapter in the specific device data sheet for availability.

26

| U-0                               | R/W-0                                                                                                                                           | U-0                                   | U-0                                  | U-0             | R/W-0                  | R/W-0            | R/W-0                |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|-----------------|------------------------|------------------|----------------------|

| _                                 | CVR2OE <sup>(1)</sup>                                                                                                                           | _                                     | _                                    | _               | VREFSEL                | BGSEL            | <1:0> <sup>(1)</sup> |

| bit 15                            |                                                                                                                                                 |                                       |                                      |                 |                        |                  | bit                  |

|                                   |                                                                                                                                                 |                                       |                                      |                 |                        |                  |                      |

| R/W-0                             | R/W-0                                                                                                                                           | R/W-0                                 | R/W-0                                | R/W-0           | R/W-0                  | R/W-0            | R/W-0                |

| CVREN                             | CVROE <sup>(2)</sup>                                                                                                                            | CVRR                                  | CVRSS <sup>(3)</sup>                 |                 | CVR<                   | :3:0>            |                      |

| bit 7                             |                                                                                                                                                 |                                       |                                      |                 |                        |                  | bit                  |

|                                   |                                                                                                                                                 |                                       |                                      |                 |                        |                  |                      |

| Legend:                           | .:4                                                                                                                                             |                                       | L:4                                  |                 | mented hit read        | aa (0)           |                      |

| R = Readable I<br>-n = Value at P |                                                                                                                                                 | W = Writable                          |                                      | 0 = 0 miniple   | mented bit, read       |                  | 0.11/2               |

|                                   | UK                                                                                                                                              | '1' = Bit is set                      |                                      |                 | eareu                  | x = Bit is unkn  | IOWI                 |

| bit 15                            | Unimplement                                                                                                                                     | t <b>ed:</b> Read as '                | 0'                                   |                 |                        |                  |                      |

| bit 14                            | -                                                                                                                                               |                                       | ge Reference                         | 2 Output Ena    | ble bit <sup>(1)</sup> |                  |                      |

|                                   |                                                                                                                                                 | •                                     | ected to the C                       | •               |                        |                  |                      |

|                                   | 0 = No voltage                                                                                                                                  | e references is                       | connected to                         | the CVREF20     | pin                    |                  |                      |

| bit 13-11                         | Unimplement                                                                                                                                     | ted: Read as '                        | 0'                                   |                 |                        |                  |                      |

| bit 10                            | VREFSEL: Vo                                                                                                                                     | •                                     | ce Select bit                        | bit             |                        |                  |                      |

|                                   | 1 = CVREFIN is<br>0 = CVREFIN is                                                                                                                |                                       | resistor netwo                       | ork             |                        |                  |                      |

| bit 9-8                           | <ul> <li>0 = CVREFIN is generated by resistor network</li> <li>BGSEL&lt;1:0&gt;: Band Gap Reference Source Select bits<sup>(1)</sup></li> </ul> |                                       |                                      |                 |                        |                  |                      |

|                                   |                                                                                                                                                 |                                       | nverting input i                     |                 |                        |                  |                      |

|                                   |                                                                                                                                                 |                                       | nverting input i                     | •               | ,                      |                  |                      |

|                                   |                                                                                                                                                 |                                       | nverting input i<br>nverting input i |                 |                        |                  |                      |

| bit 7                             |                                                                                                                                                 |                                       | e Reference E                        | •               | )                      |                  |                      |

|                                   |                                                                                                                                                 |                                       | rence circuit p                      |                 |                        |                  |                      |

|                                   | •                                                                                                                                               | •                                     | rence circuit p                      |                 |                        |                  |                      |

| bit 6                             | CVROE: Com                                                                                                                                      |                                       |                                      |                 | bit <sup>(2)</sup>     |                  |                      |

|                                   | •                                                                                                                                               | • • • •                               | is output on the                     |                 |                        |                  |                      |

| bit 5                             | •                                                                                                                                               | . ,                                   | is disconnecte<br>Reference Ra       |                 | •                      |                  |                      |

| DIL 5                             | -                                                                                                                                               | -                                     | CVRSRC/24 ste                        | -               | i Dit                  |                  |                      |

|                                   |                                                                                                                                                 |                                       | RSRC, with CV                        |                 | size                   |                  |                      |

| bit 4                             | CVRSS: Com                                                                                                                                      | parator Voltag                        | e Reference S                        | ource Selection | on bit <sup>(3)</sup>  |                  |                      |

|                                   |                                                                                                                                                 | 0                                     |                                      | · ·             | EF+) – (VREF-) or      | CVRSRC = (VR     | EF+) – (AVSS         |

|                                   |                                                                                                                                                 | •                                     | rence source,                        |                 |                        |                  |                      |

| bit 3-0                           |                                                                                                                                                 | •                                     | age Reference                        | Value Selecti   | ion $0 \le CVR3:CV$    | $R0 \le 15$ bits |                      |

|                                   | $\frac{\text{When CVRR}}{CVREFIN} = (CV)$                                                                                                       |                                       | (CVpspc)                             |                 |                        |                  |                      |

|                                   | When CVRR :                                                                                                                                     | · · · · · · · · · · · · · · · · · · · | (Crishe)                             |                 |                        |                  |                      |

|                                   | $\overline{CVREFIN} = 1/4$                                                                                                                      |                                       |                                      |                 |                        |                  |                      |

#### Register 26-6: CVRCON: Comparator Voltage Reference Control Register

- **Note 1:** This bit is not available on all devices. Refer to the "**Comparator**" or "**Op amp/Comparator**" chapter in the specific device data sheet for availability.

- 2: This bit overrides the TRIS bit setting.

- 3: Refer to the "Comparator" or "Op amp/Comparator" chapter in the specific device data sheet for available bit selections.

## 26.3 COMPARATOR OPERATION

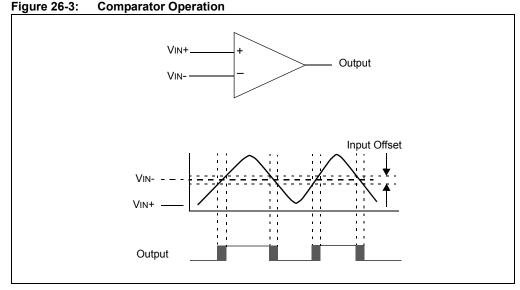

The operation of a typical comparator and the relationship between the analog input levels and the digital output are illustrated in Figure 26-3. Depending on the comparator operating mode, the monitored analog signal is compared to either an external or internal voltage reference. Each of the comparators can be configured to use the same or different reference sources. For example, one comparator can use an external reference while the others can use the internal reference. For more information on comparator operation, see 26.7 "Comparator Voltage Reference Generator".

In Figure 26-3, the external reference VIN- is a fixed external voltage. The analog signal present at VIN+ is compared to the reference signal at VIN-, and the digital output of the comparator is created by the difference between the two signals. When VIN+ is less than VIN-, the output of the comparator is a digital low level. When VIN+ is greater than VIN-, the output of the comparator is a digital high level. The shaded areas of the output represent the area of uncertainty due to input offsets and response time. The polarity of the comparator output can be inverted, so that it is a digital low level when VIN+ is greater than VIN-.

Input offset represents the range of voltage levels within which the comparator trip point can occur. The output can switch at any point in this offset range. Response time is the minimum time required for the comparator to recognize a change in input levels.

## 26.4 COMPARATOR CONFIGURATION

Each of the comparators in the Comparator or Op amp/Comparator modules is configured independently by various control bits in the following registers:

- Comparator Status (CMSTAT) register (Register 26-1)

- Comparator Control (CMxCON) register (Register 26-2)

- Comparator Mask Source Select Control (CMxMSKSRC) register (Register 26-3)

- Comparator Mask Gating Control (CMxMSKCON) register (Register 26-4)

- Comparator Filter Control (CMxFLTR) register (Register 26-5)

- Comparator Voltage Reference Control (CVRCON) register (Register 26-6)

### 26.4.1 Comparator Enable/Disable

The comparator under control may be enabled or disabled using the corresponding CON bit (CMxCON<15>). When the comparator is disabled, the corresponding trigger and interrupt generation is disabled when CON = 0.

It is recommended to first configure the CMxCON register with all bits to the desired value, and then set the CON bit (CMxCON<15>).

## 26.4.2 Comparator Output Blanking Function

In many power control and motor control applications, there are periods of time in which the inputs to the analog comparator are known to be invalid. The blanking (masking) function enables the user to ignore the comparator output during predefined periods of time. In this document, the terms 'masking' and 'blanking' are used interchangeably.

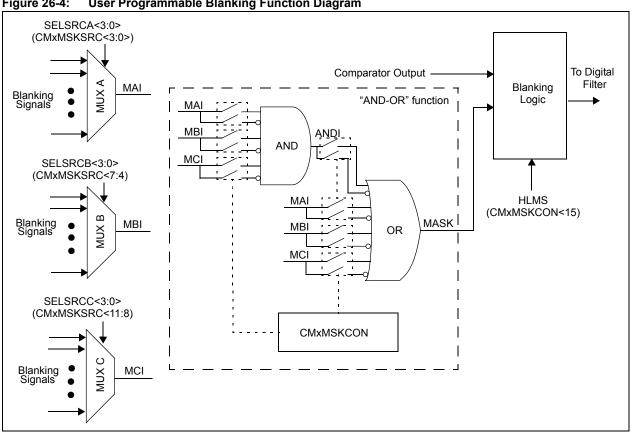

Figure 26-4 illustrates a block diagram of the comparator blanking circuitry. A blanking circuit is associated with each comparator.

Each comparator's blanking function has three user selectable inputs:

- MAI (Mask A Input)

- MBI (Mask B Input)

- MCI (Mask C Input)

The MAI, MBI and MCI signal sources are selected through the SELSRCA<3:0>, SELSRCB<3:0> and SELSRCC<3:0> bits in the CMxMSKSRC registers.

The MAI, MBI and the MCI signals are fed into an AND-OR function block, which enables the user to construct a blanking (masking) signal from these inputs. The blanking (masking) function is disabled following a system Reset.

The HLMS bits in the CMxMSKCON registers configure the masking logic to operate properly depending on the default (deasserted) state of the comparators.

If the comparator is configured for 'positive logic' so that a '0' represents a deasserted state and the comparator output is a '1' when it is asserted, the HLMS bit (CMxMSKCON<15>) should be set to '0' so that the blanking function (assuming the blanking function is active) will prevent the '1' signal of the comparator from propagating through the module.

If the comparator is configured for 'negative logic' so that a '1' represents a deasserted state and the comparator output is a '0' when it is asserted, the HLMS bit should be set to a '1' so that the blanking function (assuming blanking function is active) will prevent the '0' signal of the comparator from propagating through the module.

#### Figure 26-4: **User Programmable Blanking Function Diagram**

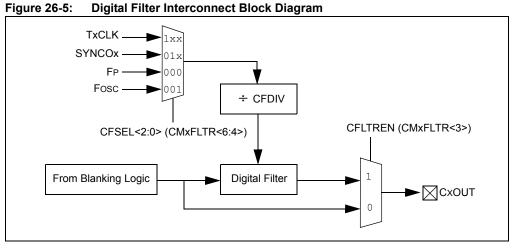

#### 26.4.3 **Digital Output Filter**

In many motor and power control applications, the comparator input signals can be corrupted by the large electromagnetic fields generated by the associated external switching power transistors. Corruption of the analog input signals to the comparator can cause unwanted comparator output transitions. The programmable digital output filter can minimize the effects of input signal corruption.

The digital filter requires three consecutive input samples to be similar before the output of the filter can change state. Assuming the current state is '0', a string of inputs such as '001010110111' will only yield an output state of '1' at the end of the example sequence after the three consecutive '1's. Similarly, a sequence of three consecutive '0's are required before the output will change to a zero state.

Because of the requirement of three similar consecutive states for the filter, the chosen digital filter clock period must be one-third or less than the maximum desired comparator response time.

The digital filter is enabled by setting the CFLTREN bit (CMxFLTR<3>). The CFDIV<2:0> bits (CMxFLTR<2:0>) select the clock divider ratio for the clock signal input to the digital filter block. The CFSEL<2:0> bits (CMxFLTR<6:4>) select the desired clock source for the digital filter. The digital filter is disabled (bypassed) following a system Reset.

## 26.4.4 Comparator Polarity Selection

To provide maximum flexibility, the output of the comparator may be inverted using the CPOL bit (CMxCON<13>). This is functionally identical to reversing the inverting and non-inverting inputs of the comparator for a particular mode.

The CPOL bit should be changed only when the comparator is disabled (CON = 0). Internal logic will prevent the generation of any corresponding triggers or interrupts when CON = 0. The logic allows both the CON and CPOL bits to be set with a single register write.

## 26.4.5 Event Polarity Selection

In addition to a programmable comparator output polarity, the Op amp/Comparator module also allows software selection for trigger/interrupt edge polarity through the EVPOL<1:0> bits in the corresponding CMxCON register. This feature allows independent control of the comparator output, as seen on any external pins, and the trigger/interrupt generation.

**Note:** The corresponding comparator must be enabled (CON = 1) for the specific trigger/interrupt generation to be enabled.

## 26.4.6 Comparator Reference Input Selection

The input to the non-inverting input of the comparator, also known as the reference input, can be selected by the value of the CREF bit (CMxCON<4>). For more information on the CREF bit, see Register 26-2.

## 26.4.7 Comparator Channel Selection

The input to the inverting input of the comparator, also known as the channel input, can be selected by the CCH<1:0> bits (CMxCON<1:0>). For more information on the CCH bits, see Register 26-2.

**Note:** Not all inputs are available for both the Op amp or Comparator modules. Refer to the **"Comparator"** or **"Op amp/Comparator"** chapter in the specific device data sheet for the available inputs.

## 26.4.8 Comparator Event Status Bit

The Comparator Event Status (CEVT) bit (CMxCON<9>) reflects whether or not the comparator has gone through the preconfigured event. After the bit is set, all future triggers and interrupts from the corresponding comparator will be blocked until the user-assigned application clears the CEVT bit. Clearing the CEVT bit begins rearming the trigger. Once the CEVT bit is cleared, it takes an extra CPU cycle for the comparator triggers to be fully rearmed.

### 26.4.9 Status Register

To provide an overview of all comparator results, the comparator output bits, CxOUT (CMxCON<8>) and event bits, CxEVT (CMxCON<9>) are replicated as status bits in the CMSTAT register.

These bits are read-only and can be altered only by manipulating the corresponding CMxCON register or the comparator input signals.

## 26.5 COMPARATOR INTERRUPTS

The Comparator Interrupt Flag (CMIF) bit (IFS1<2>) is set when the synchronized output value of any of the comparators change with respect to the last read value. The CxEVT bit in the CMSTAT register can be read by the user application to detect an event.

User-assigned software can read the CxEVT and CxOUT bits (CMxCON<9> and CMxCON<8>) to determine the change that occurred. Because it is possible to write a '1' to this register, a simulated interrupt can be software initiated. Both the CMIF and CxEVT bits must be reset by clearing them in software. These bits can be cleared in the Interrupt Service Routine (ISR). For more information, refer to **Section 6. "Interrupts"** (DS70600) in the *"dsPIC33E/PIC24E Family Reference Manual"*.

- **Note 1:** The comparison required for generating interrupts is based on the current comparator state and the last read value of the comparator outputs. Reading the CxOUT bits in the CMxCON register will update the values used for the interrupt generation.

- 2: When configured as an Op amp (OPMODE = 1) the comparator interrupts are disabled.

## 26.5.1 Interrupt Operation During Sleep Mode

If a comparator is enabled and the dsPIC33E/PIC24E device is placed in Sleep mode, the comparator remains active. If the comparator interrupt is enabled in the Interrupt module, it remains functional. Under these conditions, a comparator interrupt event will wake-up the device from Sleep mode.

Each operational comparator consumes additional current. To minimize power consumption in Sleep mode, turn off the comparators before entering Sleep mode by disabling the CON bit (CMxCON<15>). If the device wakes up from Sleep mode, the contents of the CMxCON register are not affected. For more information on Sleep mode, refer to **Section 9. "Watchdog Timer and Power-Saving Modes"** (DS70615) in the *"dsPIC33E/PIC24E Family Reference Manual"*.

### 26.5.2 Interrupt Operation During Idle Mode

The comparator remains active in Idle mode. Comparator interrupt operation during Idle mode is controlled by the Comparator Idle Mode (CMIDL) bit (CMSTAT<15>). If CMIDL = 0, normal interrupt operation continues. If CMIDL = 1, the comparator continues to operate, but it does not generate interrupts.

For more information on Idle mode, refer to **Section 9. "Watchdog Timer and Power-Saving Modes**" (DS70615) in the *"dsPIC33E/PIC24E Family Reference Manual"*.

## 26.5.3 Effects of a Reset State

A device Reset forces the CMxCON register to its Reset state, causing the comparators to be turned off (CON = 0). However, the input pins multiplexed with analog input sources are configured as analog inputs by default on a device Reset. The I/O configuration for these pins is determined by the setting of the ADxPCFGL or ADxPCFGH register. Therefore, device current is minimized when analog inputs are present at Reset time.

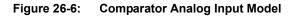

## 26.5.4 Analog Input Connection Considerations

A simplified circuit for an analog input is illustrated in Figure 26-6. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have little leakage current.

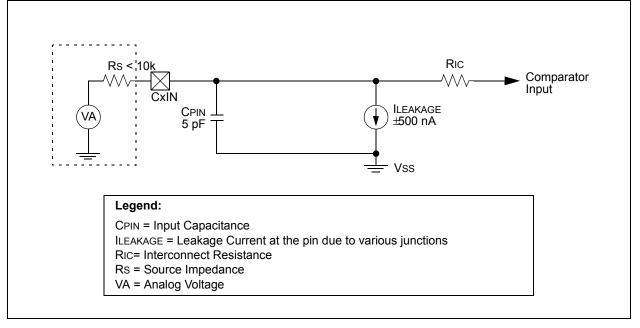

## 26.6 OP AMP CONFIGURATION

Devices with the Op amp/Comparator module can be configured as op amps by setting the OPMODE (CMxCON<10>) bit. When set, this bit enables the output of the op amp on the OAxOUT pin for the external gain/filtering components to be added in the feedback path to either of the op amp inputs.

With the proper configuration of the ADC module, the op amps can be configured such that the ADC can directly sample the output of the op amp without the need to route the op amp output to a separate analog input pin. Refer to **Section 16. "Analog-to-Digital Converter (ADC)"** (DS70621) of the *"dsPIC33E/PIC24E Family Reference Manual"* for more information on configuring the ADC. Figure 26-7 describes this configuration, which is referred to as Configuration A.

RFEEDBACK WIN R1 CXIN1-CXIN1-CXIN1+ CXIN1+ CXIN1+ CXIN1+ CXIN1+ CXIN1+ CXIN1+ CXIN1-CXIN1+ CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CXIN1-CX

Figure 26-7: Op amp Configuration A

As shown in Figure 26-8, there is a second possible configuration for the op amps, which is referred to as Configuration B. In this configuration, the op amp is not connected internally to the ADC. Instead, the op amp output is routed to a separate analog input pin (ANx). On certain device families, this configuration provides an added benefit of increasing the performance of the op amps. Refer to the **"Comparator"** or **"Op amp/Comparator"** chapter in the specific device data sheet for performance information.

Figure 26-8: Op amp Configuration B

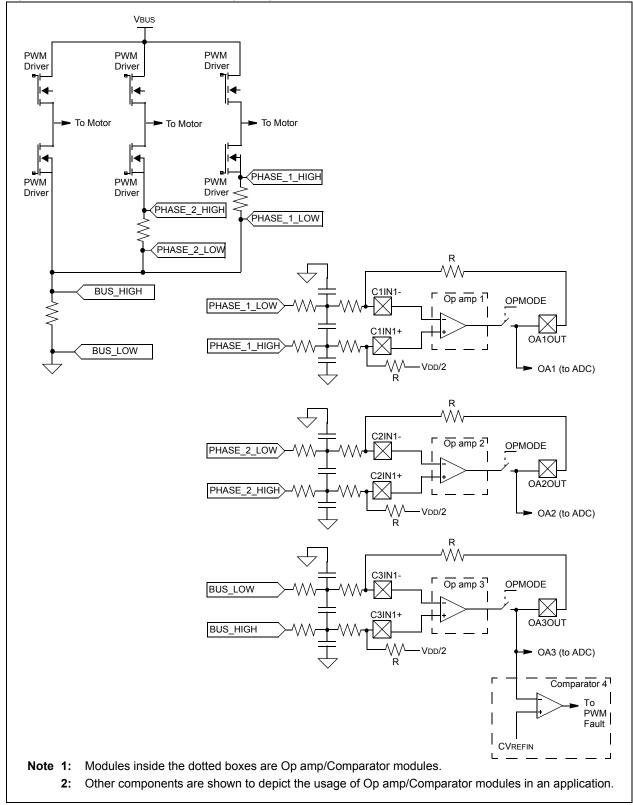

Figure 26-9 illustrates an example of a typical 3-phase motor control application taking advantage of the op amps. In this example, the op amps sample the current through the shunt resistors, with the output of the op amps connected directly to the ADC module representing Configuration A as previously described in Figure 26-7.

Figure 26-9: Op amp Application Usage Diagram

## 26.7 COMPARATOR VOLTAGE REFERENCE GENERATOR

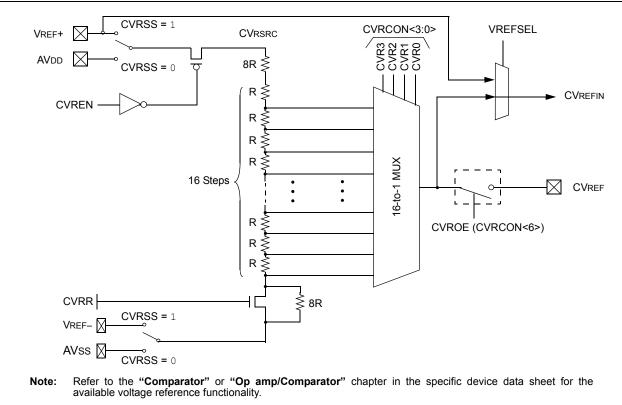

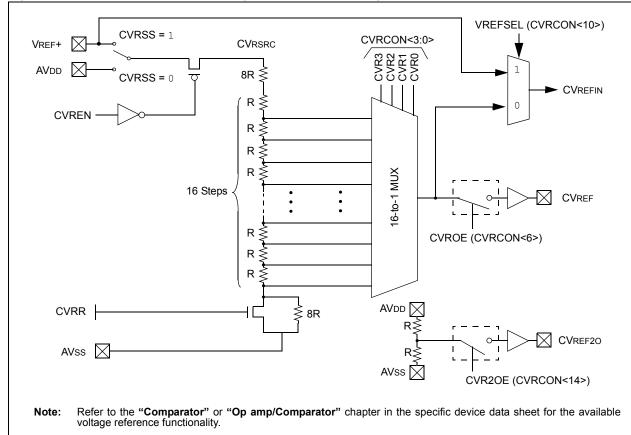

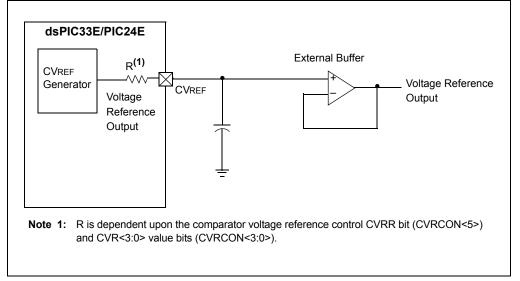

The internal comparator voltage reference is derived from a 16-tap resistor ladder network that provides a selectable voltage level, as illustrated in Figure 26-10. This resistor network generates the internal voltage reference for the analog comparators. Figure 26-11 shows the block diagram for the op amp/comparator voltage reference.

This voltage generator network is managed by the Comparator Voltage Reference Control (CVRCON) register (see Register 26-6) through these control bits:

- CVREN Comparator Voltage Reference Enable bit (CVRCON<7>) This control bit enables the voltage reference circuit.

- CVROE Comparator Voltage Reference Output Enable bit (CVRCON<6>) This control bit enables the reference voltage to be placed on the CVREF pin. When enabled, this bit overrides the corresponding TRIS bit setting.

- VREFSEL Voltage Reference Select bit (CVRCON<10>)

This control bit specifies whether the reference source is external (VREF+), or it is obtained from the 4-bit DAC output.

- CVRSS Comparator Voltage Reference Source Selection bit (CVRCON<4>) This control bit specifies that the source (CVRSS) for the voltage reference circuit is either the device voltage supply (AVDD and AVSS) or an external reference (VREF+ and VREF-).

- CVRR Comparator Voltage Reference Range Selection bit (CVRCON<5>) This control bit selects one of the two voltage ranges covered by the 16-tap resistor ladder network:

- 0 CVRSRC to 0.67 CVRSRC

- 0.25 CVRSRC to 0.75 CVRSRC

The range selected also determines the voltage increments available from the resistor ladder taps (see **26.7.1 "Configuring the Comparator Voltage Reference**").

CVR<3:0> – Comparator Voltage Reference Value Selection bits (CVRCON<3:0>) These bits designate the resistor ladder tap position.

Table 26-1 lists the voltage at each tap for both ranges with CVRSRC = 3.3V.

Figure 26-11: Op amp/Comparator Voltage Reference Block Diagram

| C)/D <2:0> | Voltage Reference |          |  |  |  |

|------------|-------------------|----------|--|--|--|

| CVR<3:0>   | <b>CVRR =</b> 0   | CVRR = 1 |  |  |  |

| 0000       | 0.83V             | 0.00V    |  |  |  |

| 0001       | 0.93V             | 0.14V    |  |  |  |

| 0010       | 1.03V             | 0.28V    |  |  |  |

| 0011       | 1.13V             | 0.41V    |  |  |  |

| 0100       | 1.24V             | 0.55V    |  |  |  |

| 0101       | 1.34V             | 0.69V    |  |  |  |